Power control (pcon), Power control (pcon) -15 – Maxim Integrated Ultra-High-Speed Flash Microcontroller User Manual

Page 23

4-15

TSL

Bit 5

AID

Bit 4

Bits 3, 2, 1

SEL

Bit 0

Toggle Select. When clear (= 0), DPTR-related instructions do not affect the SEL bit. When set

(= 1), the SEL bit is toggled following execution of any of the below DPTR-related instructions:

INC DPTR

MOV DPTR, #data16

MOVC A, @A+DPTR

MOVX A, @DPTR

MOVX @DPTR, A

Autoincrement/Decrement Enable. When set, the active data pointer is automatically increment-

ed or decremented (as determined by ID1, ID0 bit settings) following execution of any of the below

DPTR-related instructions:

MOVC A, @A+DPTR

MOVX A, @DPTR

MOVX @DPTR, A

Reserved. These bits read 010b.

Data Pointer Select. This bit selects the active data pointer.

0 = Instructions that use the DPTR use DPL and DPH.

1 = Instructions that use the DPTR use DPL1 and DPH1.

SMOD_0

Bit 7

SMOD0

Bit 6

OFDF

Bit 5

OFDE

Bit 4

GF1

Bit 3

GF0

Bit 2

Serial Port 0 Baud Rate Doubler Enable. This bit enables/disables the serial baud rate doubling

function for Serial Port 0.

0 = Serial Port 0 baud rate is that defined by baud rate generation equation.

1 = Serial Port 0 baud rate is double that defined by baud rate generation equation.

Framing Error Detection Enable. When clear (= 0), SCON1.7 and SCON0.7 serve as mode select

bit SM0 for the respective serial ports. When set (= 1), SCON1.7 and SCON0.7 report whether a

Framing Error has been detected.

Oscillator Fail Detect Flag. When OFDE = 1, this flag will be set if a reset condition is generated

due to oscillator failure. This bit is cleared on a power-on reset and is unchanged by other reset

sources. This bit must be cleared by software.

Oscillator Fail Detect Enable. When set (= 1), the oscillator fail detect circuitry and flag genera-

tion are enabled. An oscillator fail detection occurs if the crystal oscillator falls below ~20kHz. An

oscillator fail detection does not occur if the oscillator is halted through software setting of the STOP

bit (PCON.1) or when running from the internal ring oscillator source. When clear (= 0), the oscil-

lator fail detect circuitry is disabled.

General-Purpose User Flag 1. This is a general-purpose flag for software control.

General-Purpose User Flag 0. This is a general-purpose flag for software control.

R = Unrestricted read, W = Unrestricted write, -n = Value after reset, * = See description

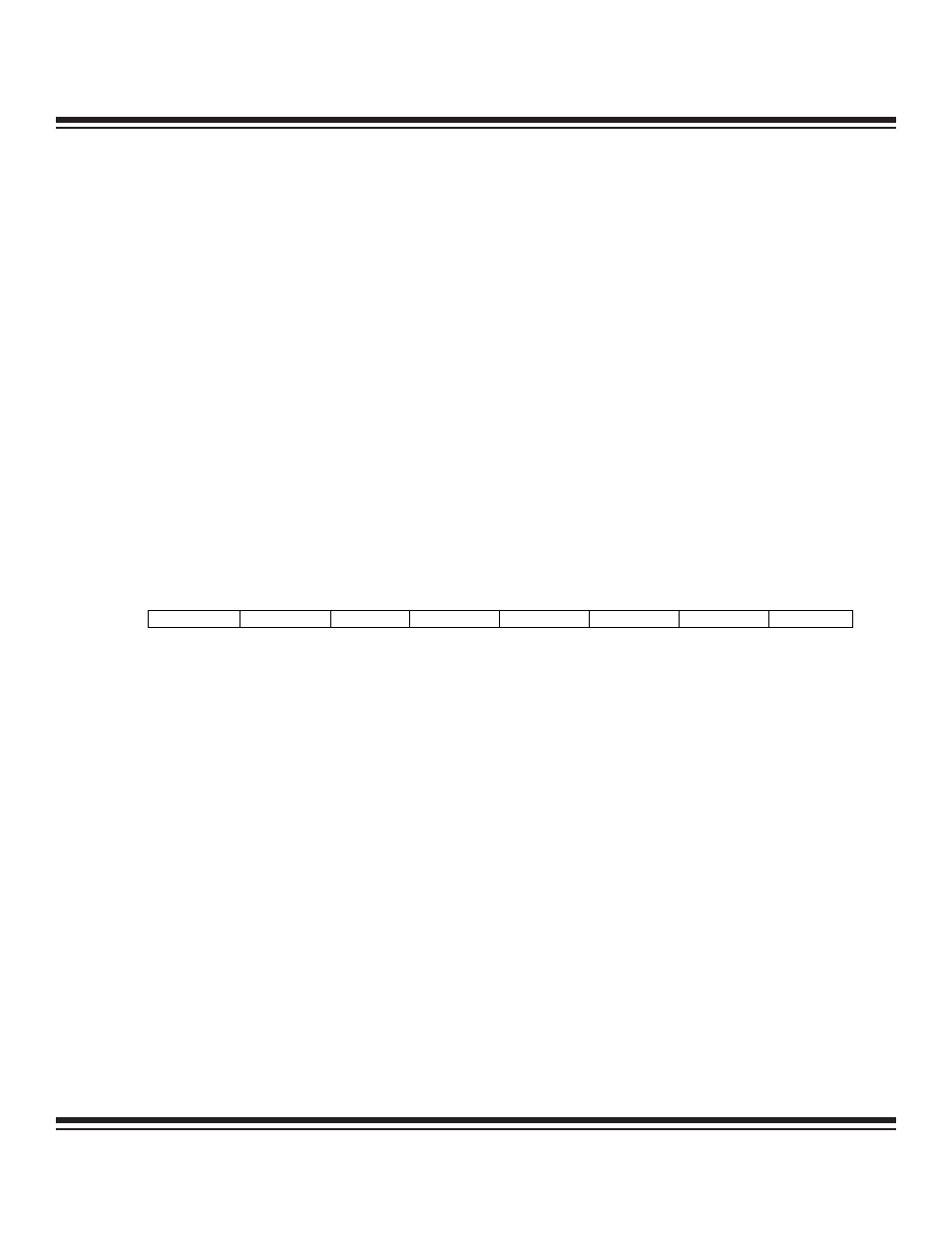

Power Control (PCON)

7

6

5

4

3

2

1

0

SFR 87h

SMOD_0

SMOD0

OFDF

OFDE

GF1

GF0

STOP

IDLE

RW-0

RW-0

RW-0*

RW-0*

RW-0

RW-0

RW-0

RW-0

Ultra-High-Speed Flash

Microcontroller User’s Guide

Maxim Integrated