Avalon-st packets to pci express tlps, Avalon-st packets to pci express tlps -22 – Altera Arria 10 Avalon-ST User Manual

Page 88

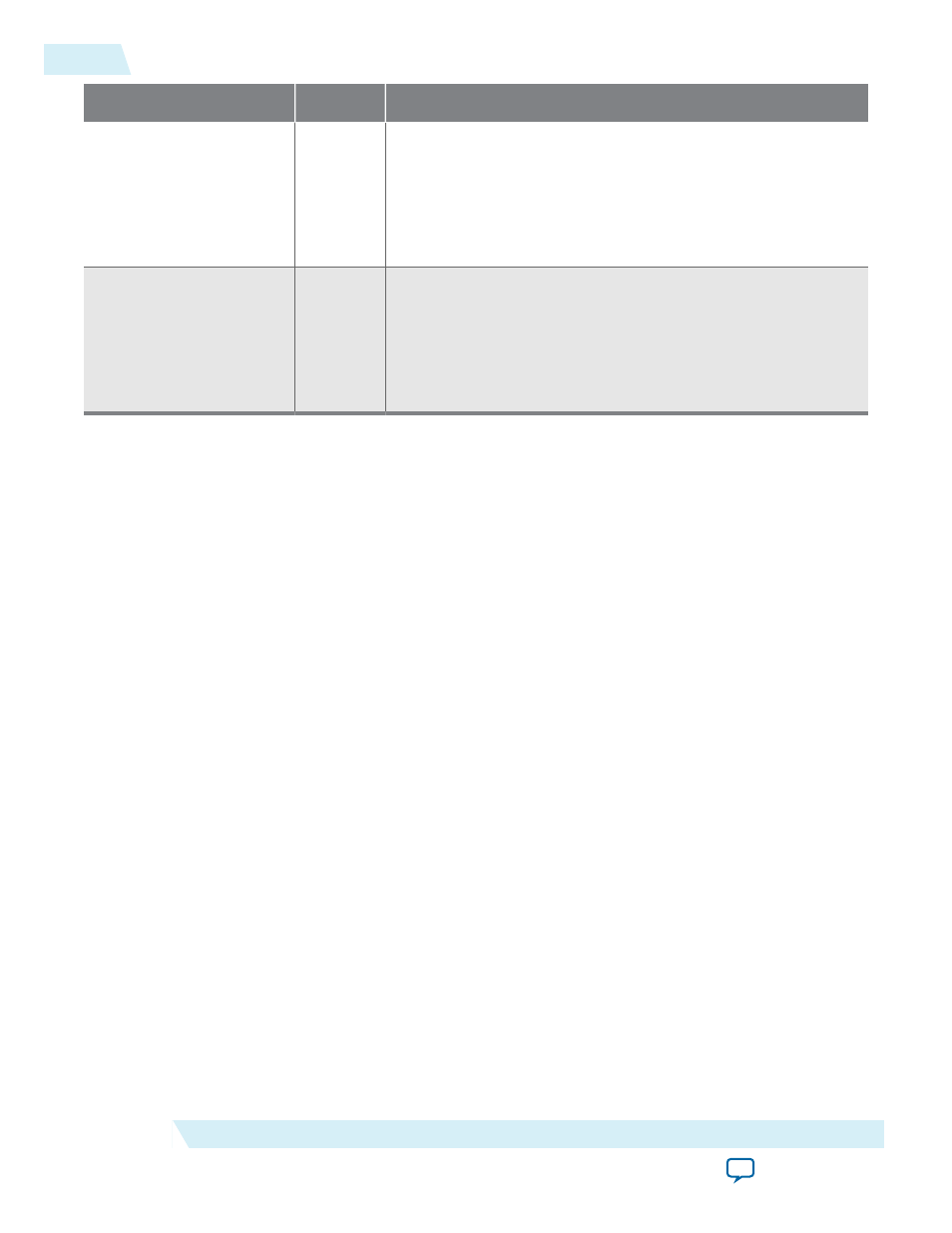

Signal

Direction

Description

ko_cpl_spc_

header[7:0]

Output

The Application Layer can use this signal to build circuitry to

prevent RX buffer overflow for completion headers. Endpoints

must advertise infinite space for completion headers; however,

RX buffer space is finite.

ko_cpl_spc_header

is a static signal

that indicates the total number of completion headers that can be

stored in the RX buffer.

ko_cpl_spc_data[11:0]

Output

The Application Layer can use this signal to build circuitry to

prevent RX buffer overflow for completion data. Endpoints must

advertise infinite space for completion data; however, RX buffer

space is finite.

ko_cpl_spc_data

is a static signal that reflects the

total number of 16 byte completion data units that can be stored

in the completion RX buffer.

Attention: If you instantiate this IP core as a separate component from the Quartus II IP Catalog, the

Message pane reports the following warning messages:

pcie_a10.pcie_a10_hip_0.tx.st Interface must have an associated reset

pcie_a10.pcie_a10_hip_0.rx.st Interface must have an associated reset

You can safely ignore these warnings because the IP core has a dedicated hard reset pin that is

not part of the Avalon-ST TX or RX interface.

Related Information

•

Data Alignment and Timing for the 64-Bit Avalon-ST TX Interface

•

Data Alignment and Timing for the 128-Bit Avalon-ST TX Interface

on page 6-25

•

Data Alignment and Timing for the 256-Bit Avalon-ST TX Interface

on page 6-28

Avalon-ST Packets to PCI Express TLPs

The following figures illustrate the mappings between Avalon-ST packets and PCI Express TLPs. These

mappings apply to all types of TLPs, including posted, non-posted, and completion TLPs. Message TLPs

use the mappings shown for four dword headers. TLP data is always address-aligned on the Avalon-ST

interface whether or not the lower dwords of the header contains a valid address, as may be the case with

TLP type (message request with data payload).

For additional information about TLP packet headers, refer to Section 2.2.1 Common Packet Header Fields

in the PCI Express Base Specification .

Data Alignment and Timing for the 64‑Bit Avalon-ST TX Interface

The following figure illustrates the mapping between Avalon-ST TX packets and PCI Express TLPs for

three dword header TLPs with non-qword aligned addresses on a 64-bit bus.

6-22

Avalon-ST Packets to PCI Express TLPs

UG-01145_avst

2015.05.04

Altera Corporation

Interfaces and Signal Descriptions