Pci express and pci capabilities parameters, Pci express and pci capabilities parameters -8 – Altera Arria 10 Avalon-ST User Manual

Page 51

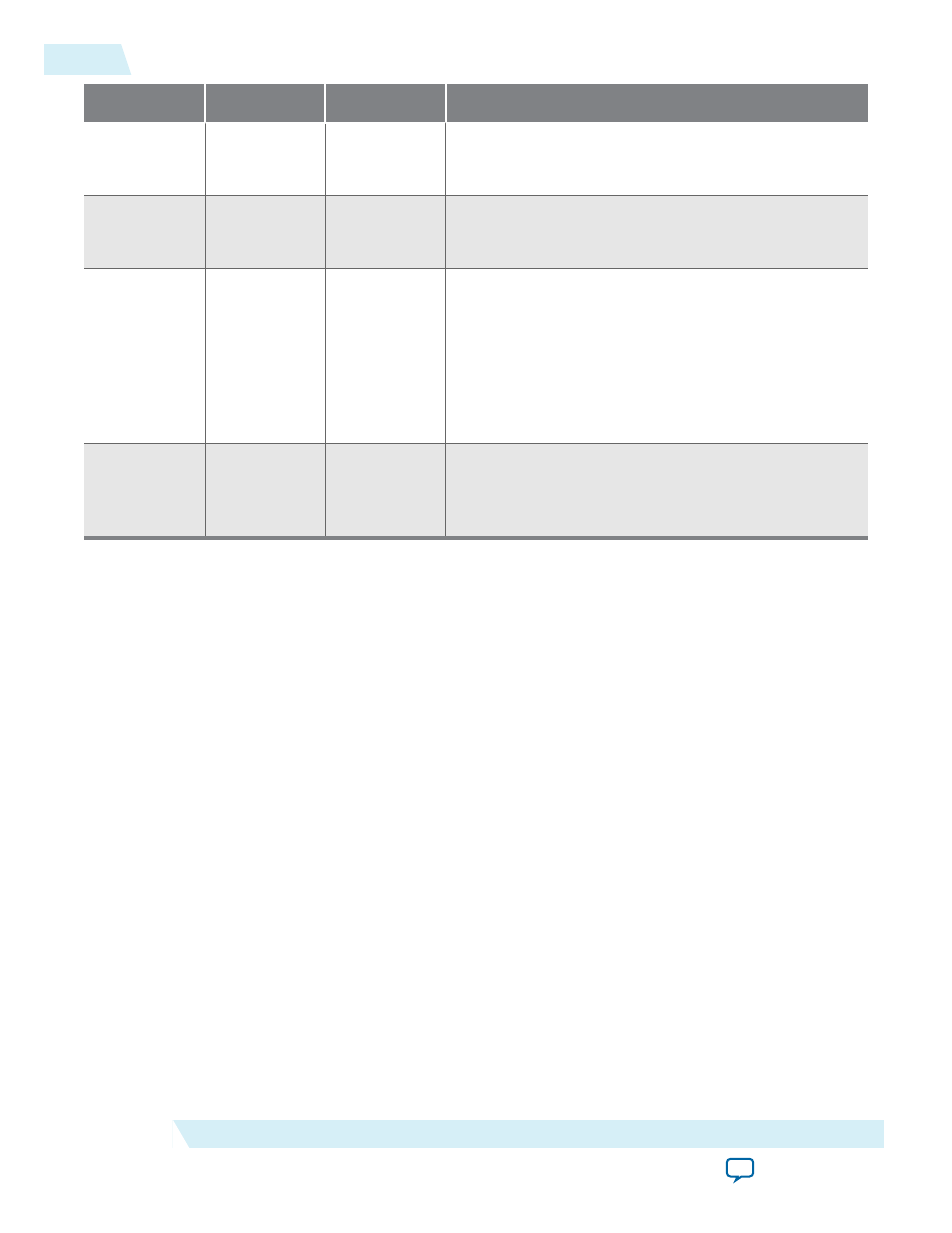

Register Name

Range

Default Value

Description

Revision ID

8 bits

0x00000000

Sets the read-only value of the

Revision ID

register.

Address offset: 0x008.

Class code

24 bits

0x00000000

Sets the read-only value of the

Class Code

register.

Address offset: 0x008.

Subsystem

Vendor ID

16 bits

0x00000000

Sets the read-only value of the

Subsystem Vendor ID

register in the PCI Type 0 Configuration Space. This

parameter cannot be set to 0xFFFF per the PCI Express

Base Specification. This value is assigned by PCI-SIG to

the device manufacturer. This register is only valid in

the Type 0 (Endpoint) Configuration Space.

Address offset: 0x02C.

Subsystem

Device ID

16 bits

0x00000000

Sets the read-only value of the

Subsystem Device ID

register in the PCI Type 0 Configuration Space.

Address offset: 0x02C

At run time, you can change the values of these registers using the optional reconfiguration block signals.

Related Information

•

on page 16-1

•

PCI Express and PCI Capabilities Parameters

This group of parameters defines various capability properties of the IP core. Some of these parameters

are stored in the PCI Configuration Space - PCI Compatible Configuration Space. The byte offset

indicates the parameter address.

4-8

PCI Express and PCI Capabilities Parameters

UG-01145_avst

2014.08.18

Altera Corporation

Parameter Settings