Clocks, Clock domains, Clocks -4 – Altera Arria 10 Avalon-ST User Manual

Page 147: Clock domains -4

For descriptions of the available reset signals, refer to Reset Signals, Status, and Link Training Signals.

Related Information

Reset, Status, and Link Training Signals

Clocks

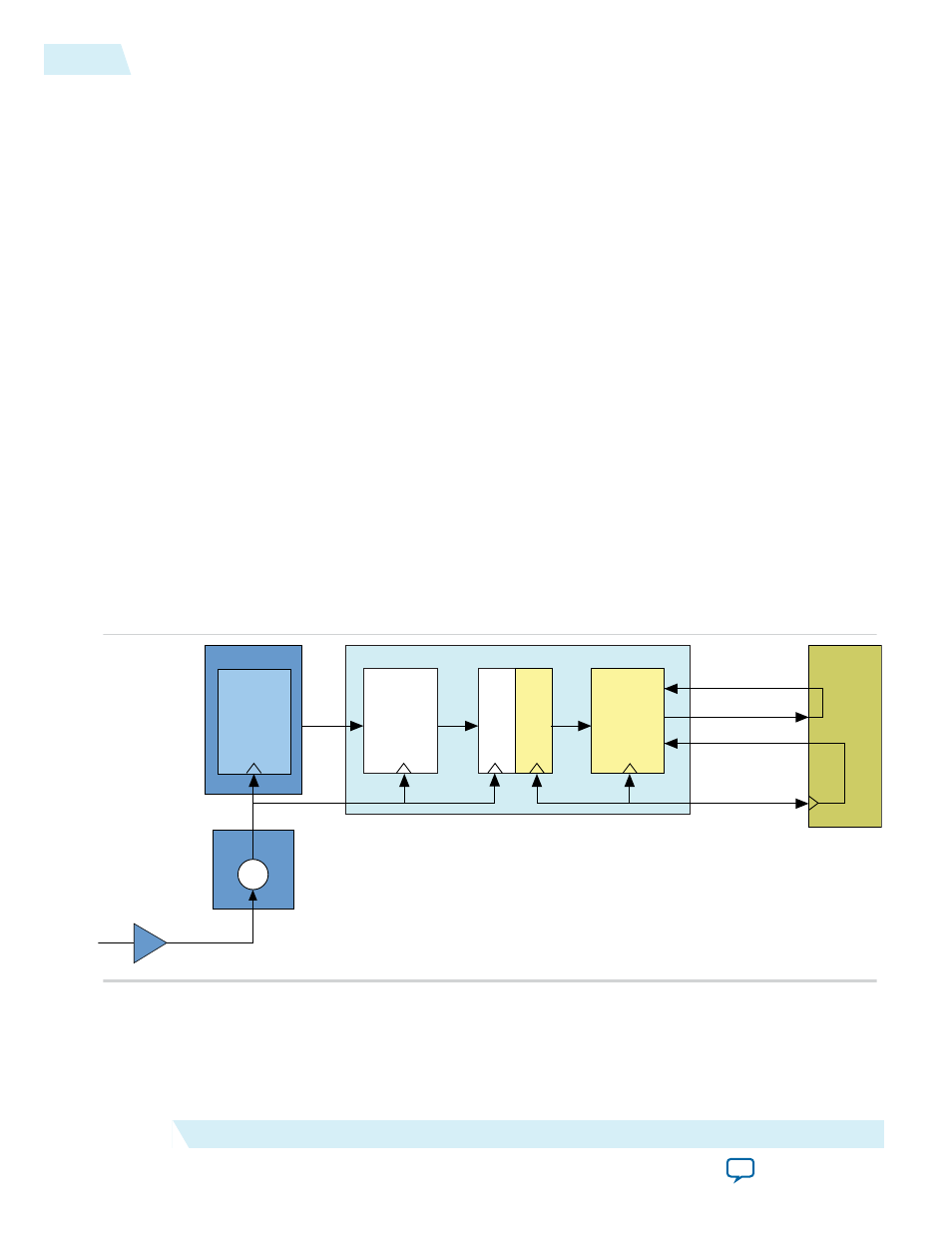

The Hard IP contains a clock domain crossing (CDC) synchronizer at the interface between the

PHY/MAC and the DLL layers. The synchronizer allows the Data Link and Transaction Layers to run at

frequencies independent of the PHY/MAC. The CDC synchronizer provides more flexibility for the user

clock interface. Depending on parameters you specify, the core selects the appropriate

coreclkout_hip

.

You can use these parameters to enhance performance by running at a higher frequency for latency

optimization or at a lower frequency to save power.

In accordance with the PCI Express Base Specification, you must provide a 100 MHz reference clock that is

connected directly to the transceiver.

Related Information

Clock Domains

Figure 8-5: Clock Domains and Clock Generation for the Application Layer

The following illustrates the clock domains when using

coreclkout_hip

to drive the Application Layer

and the

pld_clk

of the IP core. The Altera-provided example design connects

coreclkout_hip

to the

pld_clk

. However, this connection is not mandatory.

100 MHz

refclk

pclk

Hard IP for PCI Express

PHY/MAC

Clock

Domain

Crossing

(CDC)

Data Link

and

Transaction

Layers

TX PLL

PCS

pclk

coreclkout_hip

Application

Layer

pld_clk

(62.5, 125

or 250 MHz)

serdes_pll_locked

pld_core_ready

Transceiver

8-4

Clocks

UG-01145_avst

2015.05.04

Altera Corporation

Arria 10 Reset and Clocks