Interfaces and signal descriptions, Interfaces and signal descriptions -1 – Altera Arria 10 Avalon-ST User Manual

Page 67

Interfaces and Signal Descriptions

6

2015.05.04

UG-01145_avst

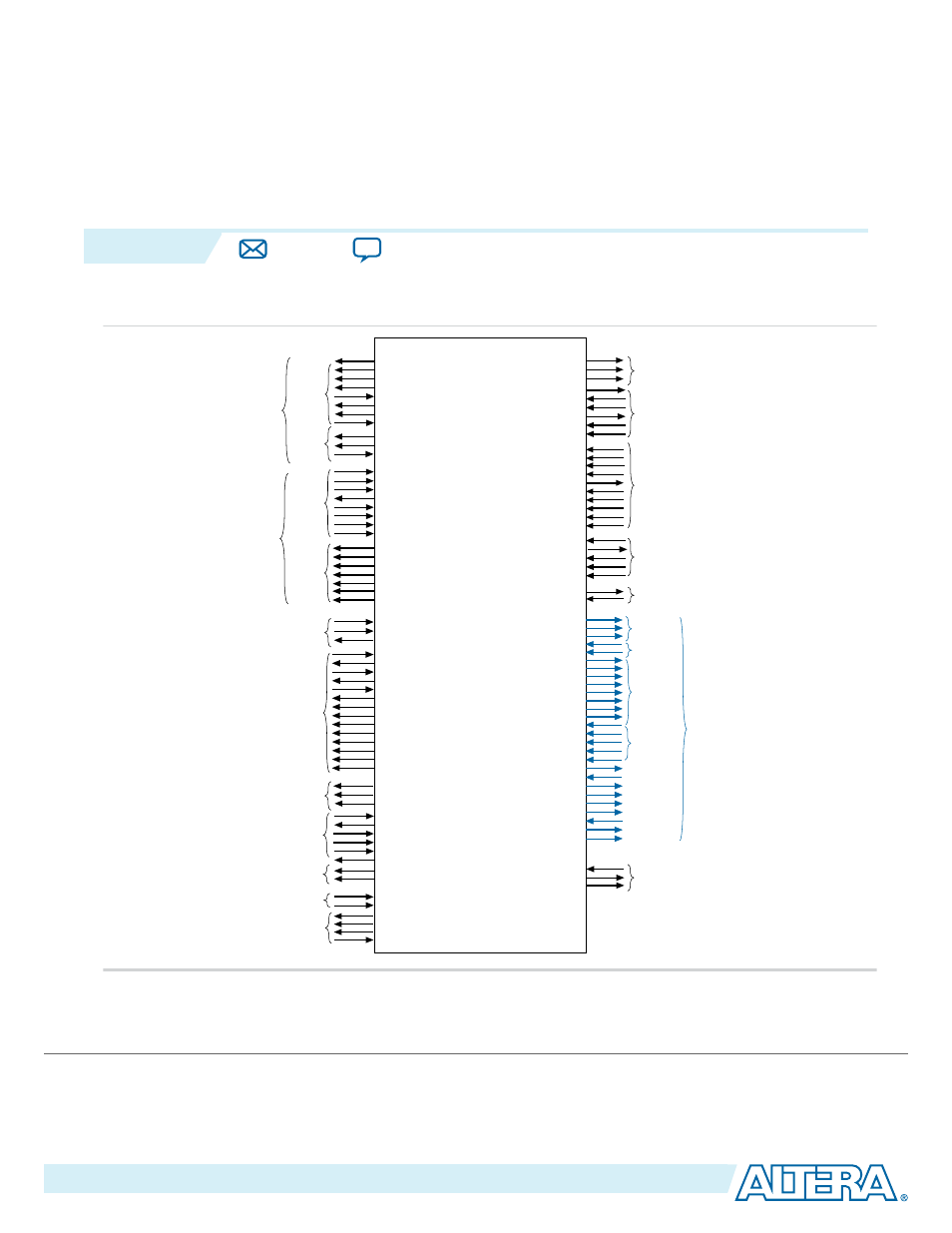

Figure 6-1: Avalon-ST Hard IP for PCI Express Top-Level Signals

rx_st_data[63:0], [127:0], [255:0]

rx_st_sop, [1:0]

rx_st_eop, [1:0]

rx_st_empty[1:0]

rx_st_ready

rx_st_valid

rx_st_err

rx_st_mask

rx_st_bar[7:0]

rx_st_parity[7:0], [15:0], [31:0]

rxfc_cplbuf_ovf

Hard IP for Express, Avalon-ST Interface

Test

Interface

tx_st_data[63:0], [127:0], [255:0]

tx_st_sop, [1:0]

tx_st_eop, [1:0]

tx_st_ready

tx_st_valid

tx_st_empty[1:0]

tx_st_err

tx_st_parity[7:0], [15:0], [31:0]

tx_cred_data_fc[11:0]

tx_cred_fc_hip_cons[5:0]

tx_cred_fc_infinite[5:0]

tx_cred_hdr_fc[7:0]

ko_cpl_spc_header[7:0]

ko_cpl_spc_data[11:0]

Clocks

TX Port

RX Port

Parity Error

Power

Managementt

LMI

test_in[31:0]

testin_zero

lane_act[3:0]

tl_cfg_add[3:0]

tl_cfg_ctl[31:0]

tl_cfg_sts[52:0]

hpg_ctrler[4:0]

lmi_dout[7:0]

lmi_rden

lmi_wren

lmi_ack

lmi_addr[11:0]

lmi_din[7:0]

Hard IP

Reconfiguration

(Optional)

tx_out[7:0]

rx_in[7:0]

Serial IF to PIPE

Avalon-ST

Avalon-ST

Component

Specific

Component

Specific

TX

Credit

derr_cor_ext_rcv

derr_rpl

derr_cor_ext_rpl

int_status[3:0]

serr_out

cpl_err[6:0]

cpl_pending

tx_par_err[1:0]

rx_par_err

cfg_par_err

hip_reconfig_clk

hip_reconfig_rst_n

hip_reconfig_address[9:0]

hip_reconfig_read

hip_reconfig_readdata[15:0]

hip_reconfig_write

hip_reconfig_writedata[15:0]

hip_reconfig_byte_en[1:0]

ser_shift_load

interface_sel

npor

reset_status

pin_perst

serdes_pll_locked

pld_core_ready

pld_clk_inuse

dlup

dlup_exit

rev128ns

ev1us

hotrst_exit

l2_exit

current_speed[1:0]

ltssmstate[4:0]

Reset &

Link Status

ECC Error

Completion

Interface

Transaction Layer

Configuration

Interrupts

for Root Ports

Interrupt

for Endpoints

app_msi_req

app_msi_ack

app_msi_tc[2:0]

app_msi_num[4:0]

app_int_sts

app_int_ack

pme_to_cr

pme_to_sr

pm_event

pm_data[9:0]

pm_auxpwr

refclk

pld_clk

coreclkout_hip

txdata0[7:0]

txdatak0

txdatavalid0

rxdata0[7:0]

rxdatak0

txdetectrx0

txelectidle0

txcompl0

rxpolarity0

powerdown0[1:0]

txmargin[2:0]

txswing

rxvalid0

phystatus0

rxelecidle0

rxstatus0[2:0]

simu_mode_pipe

sim_pipe_rate[1:0]

sim_pipe_pclk_in

sim_pipe_pclk_out

sim_pipe_clk250_out

sim_pipe_clk500_out

sim_ltssmstate[4:0]

rxfreqlocked0

eidleinfersel0[2:0]

txdeemph0

Transmit Data

Interface Signals

Receive Data

Interface Signals

Command

Interface Signals

Status

Interface Signals

tx_cred_fc_sel[1:0]

PIPE

Interface

for Simulation

and Hardware

Debug Using

dl_ltssm[4:0]

in SignalTap,

©

2015 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, ENPIRION, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at

www.altera.com/common/legal.html

. Altera warrants performance

of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information,

product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device

specifications before relying on any published information and before placing orders for products or services.

www.altera.com

101 Innovation Drive, San Jose, CA 95134