Altera Arria 10 Avalon-ST User Manual

Page 32

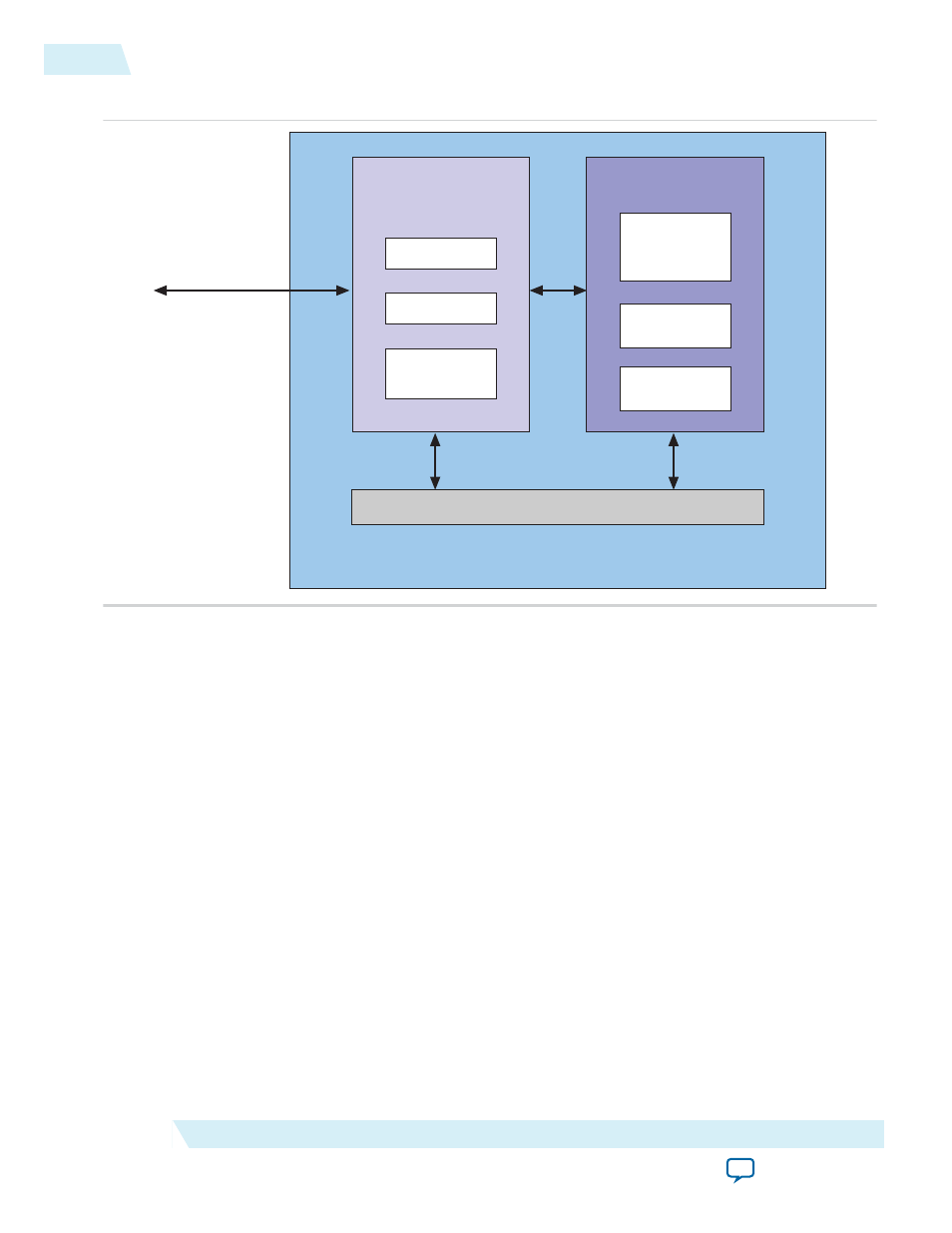

Figure 3-1: Configuration Bypass Mode Qsys Example Design

to PCIe Root Port

and Host System

Configuration

Bypass Top

(cfbp_top)

APPS: Config Bypass Example

Root Port

(cfbp_app_example)

DUT: Hard IP for PCIe

Using Configuration Bypass

Mode Endpoint

Function 0

Function 1

2 MByte Memory

Reset

(rs_hip)

Configuration Space

Configuration Space

Local Management

Interface (LMI)

Function 0 Registers

Function 1 Registers

pcie_reconfig_driver_0

Copying the Configuration Space Bypass Mode Example Design

Follow these steps to copy the Configuration Space Bypass Mode Qsys Example Design to your working

directory:

1. Copy the example design,

pcie_cfbp_g2x8_ast256.qsys

, from the installation directory

altera/altera_pcie/altera_pcie_a10_ed/example_design/a10

to your working directory.

2. Copy the Qsys wrapper file for the Configuration Space Bypass application logic,

altera_pcie_cfgbp_ed_

hw.tcl

, from the installation directory

a10

to your working directory.

3. Rename the

pcie_cfbp_g2x8_ast256.qsys top.qys

. Renaming is necessary because the testbench defines

top.v

as the top-level wrapper. Qsys creates

top.v

from

top.qsys

when you generate the system.

4. Start Qsys by typing

qsys-edit

and open

top.qsys

when prompted by Qsys.

The following figure shows the complete system.

3-2

Copying the Configuration Space Bypass Mode Example Design

UG-01145_avst

2014.08.18

Altera Corporation

Getting Started with the Configuration Space Bypass Mode Qsys Example Design