Generating the testbench, Simulating the example design, Generating the testbench -3 – Altera Arria 10 Avalon-ST User Manual

Page 22: Simulating the example design -3

The example design includes the following components:

• DUT—This is Gen1 ×8 Endpoint. For your own design, you can select the data rate, number of lanes,

and either Endpoint or Root Port mode.

• APPS—This Root Port BFM configures the DUT and drives read and write TLPs to test DUT

functionality. An Endpoint BFM is available if your PCI Express design implements a Root Port.

Generating the Testbench

1. On the Generate menu, select Generate Testbench System. Specify the parameters listed in the

following table.

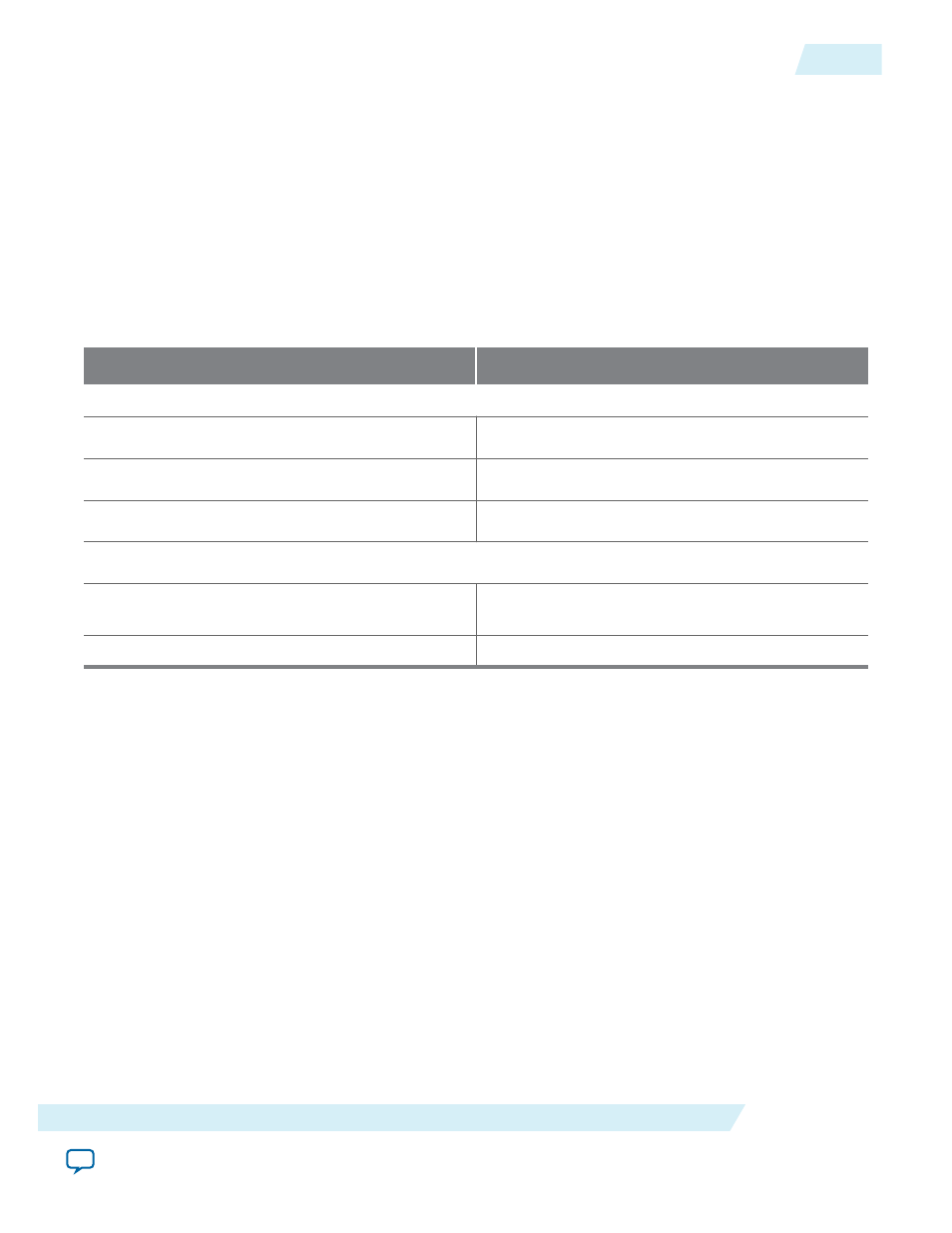

Table 2-1: Parameters to Specify on the Generation Tab in Qsys

Parameter

Value

Testbench System

Create testbench Qsys system

Standard, BFMs for standard Qsys interfaces

Create testbench simulation model

Verilog

Allow mixed-language simulation

Turn this option off

Output Directory

Clear output directories for selected generation

targets

Turn this option off

Testbench

2. Click the Generate button at the bottom of the Generation tab to create the testbench.

Note: This testbench assumes that you are running the DMA application that the example design

available in the installation directory creates. Otherwise, the testbench tests will probably fail unless

your own testbench has equivalent functionality.

Simulating the Example Design

1. Start your simulation tool. This example uses the ModelSim

®

software.

2. From the ModelSim transcript window, in the testbench directory,

tb/sim/mentor

, type the following commands:

a.

do msim_setup.tcl

b.

ld_debug

(This command compiles all design files and elaborates the top-level design without any

optimization.)

c.

run -all

UG-01145_avst

2015.05.04

Generating the Testbench

2-3

Getting Started with the Arria 10 Hard IP for PCI Express

Altera Corporation