Altera Arria 10 Avalon-ST User Manual

Page 72

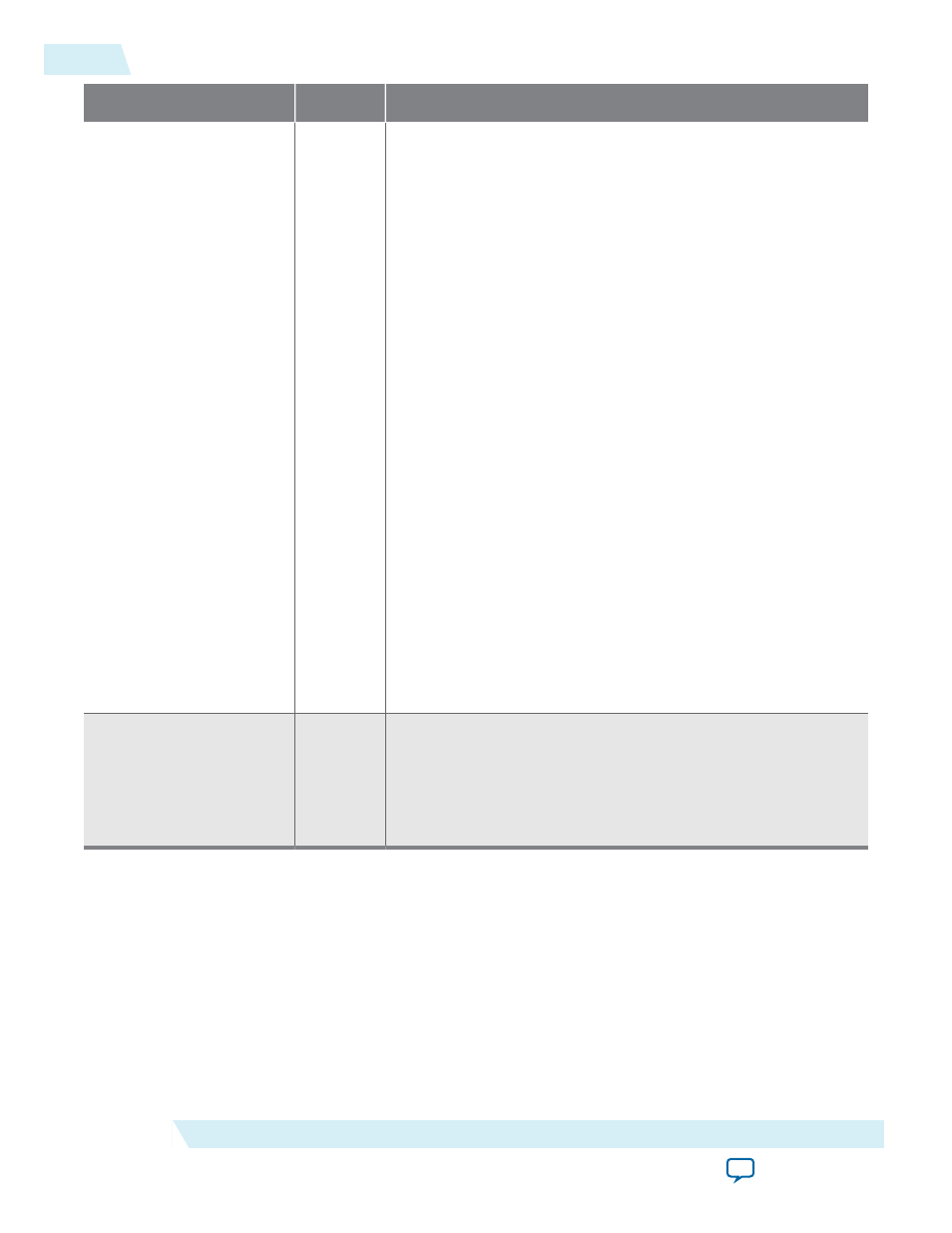

Signal

Direction

Description

rx_st_be[

Output

Byte enables corresponding to the

rx_st_data

. The byte enable

signals only apply to PCI Express Memory Write and I/O Write

TLP payload fields. When using 64-bit Avalon-ST bus, the width

of

rx_st_be

is 8 bits. When using 128-bit Avalon-ST bus, the

width of

rx_st_be

is 16 bits. This signal is optional. You can

derive the same information by decoding the

FBE

and

LBE

fields

in the TLP header. The byte enable bits correspond to data bytes

as follows:

•

rx_st_data[127:120]

=

rx_st_be[15]

•

rx_st_data[119:112]

=

rx_st_be[14]

•

rx_st_data[111:104]

=

rx_st_be[13]

•

rx_st_data[95:88]

=

rx_st_be[12]

•

rx_st_data[87:80]

=

rx_st_be[11]

•

rx_st_data[79:72]

=

rx_st_be[10]

•

rx_st_data[71:64]

=

rx_st_be[9]

•

rx_st_data[7:0]

=

rx_st_be[8]

•

rx_st_data[63:56]

=

rx_st_be[7]

•

rx_st_data[55:48]

=

rx_st_be[6]

•

rx_st_data[47:40]

=

rx_st_be[5]

•

rx_st_data[39:32]

=

rx_st_be[4]

•

rx_st_data[31:24]

=

rx_st_be[3]

•

rx_st_data[23:16]

=

rx_st_be[2]

•

rx_st_data[15:8]

=

rx_st_be[1]

•

rx_st_data[7:0]

=

rx_st_be[0]

This signal is deprecated.

rx_st_parity[

Output

The IP core generates byte parity when you turn on Enable byte

parity ports on Avalon-ST interface on the System Settings tab

of the parameter editor. Each bit represents odd parity of the

associated byte of the

rx_st_data

rx_st_data bus. For example,

bit[0] corresponds to

rx_st_data[7:0]

rx_st_data[7:0], bit[1]

corresponds to

rx_st_data[15:8]

.

For more information about the Avalon-ST protocol, refer to the Avalon Interface Specifications.

Related Information

Data Alignment and Timing for the 64‑Bit Avalon‑ST RX Interface

To facilitate the interface to 64-bit memories, the Arria 10 Hard IP for PCI Express aligns data to the

qword or 64 bits by default. Consequently, if the header presents an address that is not qword aligned, the

Hard IP block shifts the data within the qword to achieve the correct alignment.

6-6

Data Alignment and Timing for the 64‑Bit Avalon‑ST RX Interface

UG-01145_avst

2015.05.04

Altera Corporation

Interfaces and Signal Descriptions