Altera Arria 10 Avalon-ST User Manual

Page 85

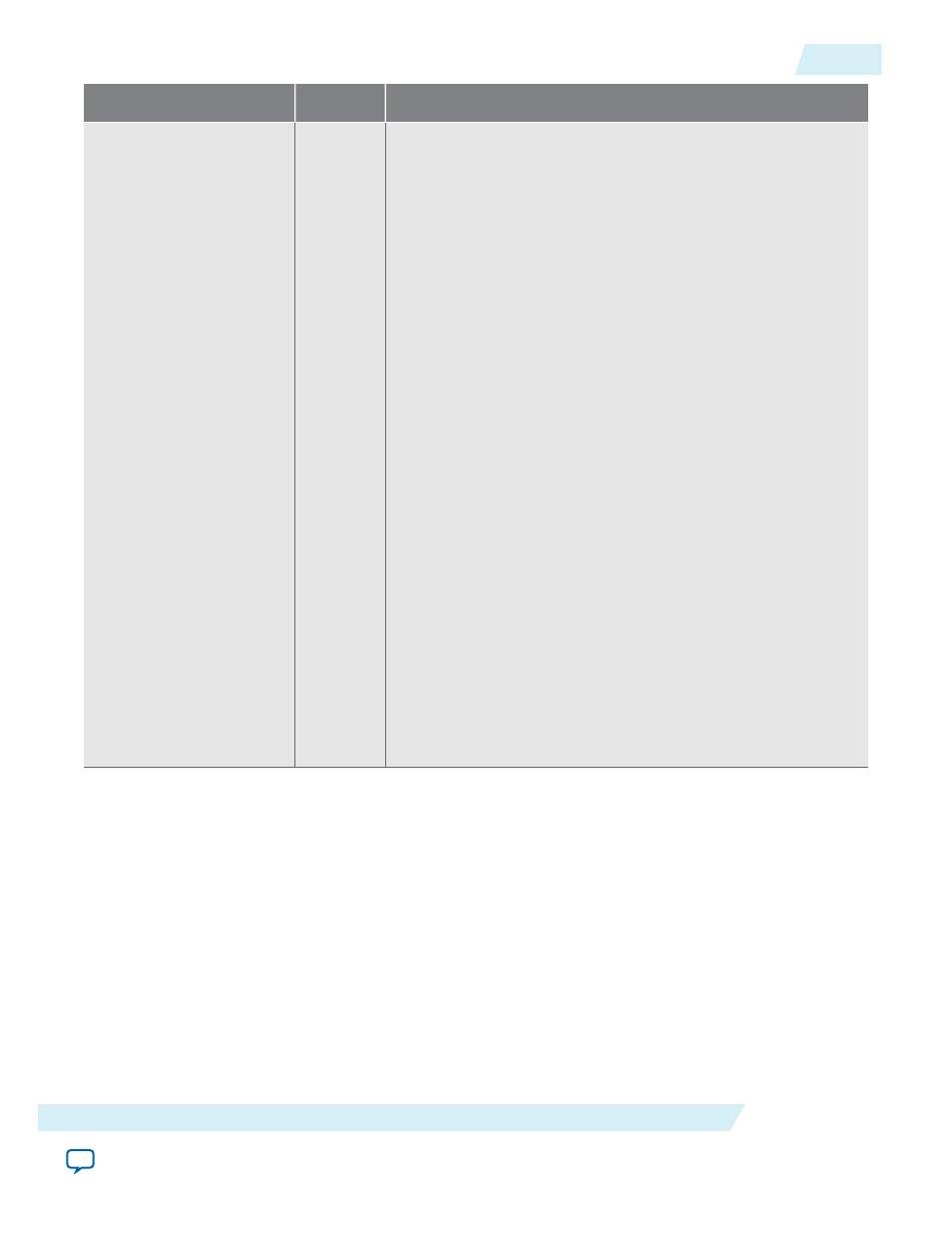

Signal

Direction

Description

words that contain data, resulting in the following encodings for

the 128-and 256-bit interfaces:

128-Bit interface:

tx_st_empty

= 0,

tx_st_data[127:0]

contains

valid data

tx_st_empty

= 1,

tx_st_data[63:0]

contains valid

data

256-bit interface:

tx_st_empty

= 0,

tx_st_data[255:0]

contains

valid data

tx_

st_empty

= 1,

tx_st_data[191:0]

contains valid

data

tx_st_empty

= 2,

tx_st_data[127:0]

contains valid

data

tx_st_empty

= 3,

tx_st_data[63:0]

contains valid data

For 256-bit data, when you turn on Enable multiple packets per

cycle, the following correspondences apply:

• bit 1 applies to the eop occurring in rx_st_data[255:128]

• bit 0 applies to the eop occurring in rx_st_data[127:0]

When the TLP ends in the lower 128bits, the following equations

apply:

•

tx_st_eop[0]=1 & tx_st_empty[0]=0

,

tx_st_

data[127:0]

contains valid data

•

tx_st_eop[0]=1 & tx_st_empty[0]=1

,

tx_st_data[63:0]

contains valid data,

tx_st_data[127:64]

is empty

When TLP ends in the upper 128bits, the following equations

apply:

•

tx_st_eop[1]=1 & tx_st_empty[1]=0

,

tx_st_

data[255:128]

contains valid data

•

tx_st_eop[1]=1 & tx_st_empty[1]=1

,

tx_st_

data[191:128]

contains valid data,

tx_st_data[255:192]

is

empty

UG-01145_avst

2015.05.04

Avalon-ST TX Interface

6-19

Interfaces and Signal Descriptions

Altera Corporation