Altera Arria 10 Avalon-ST User Manual

Page 124

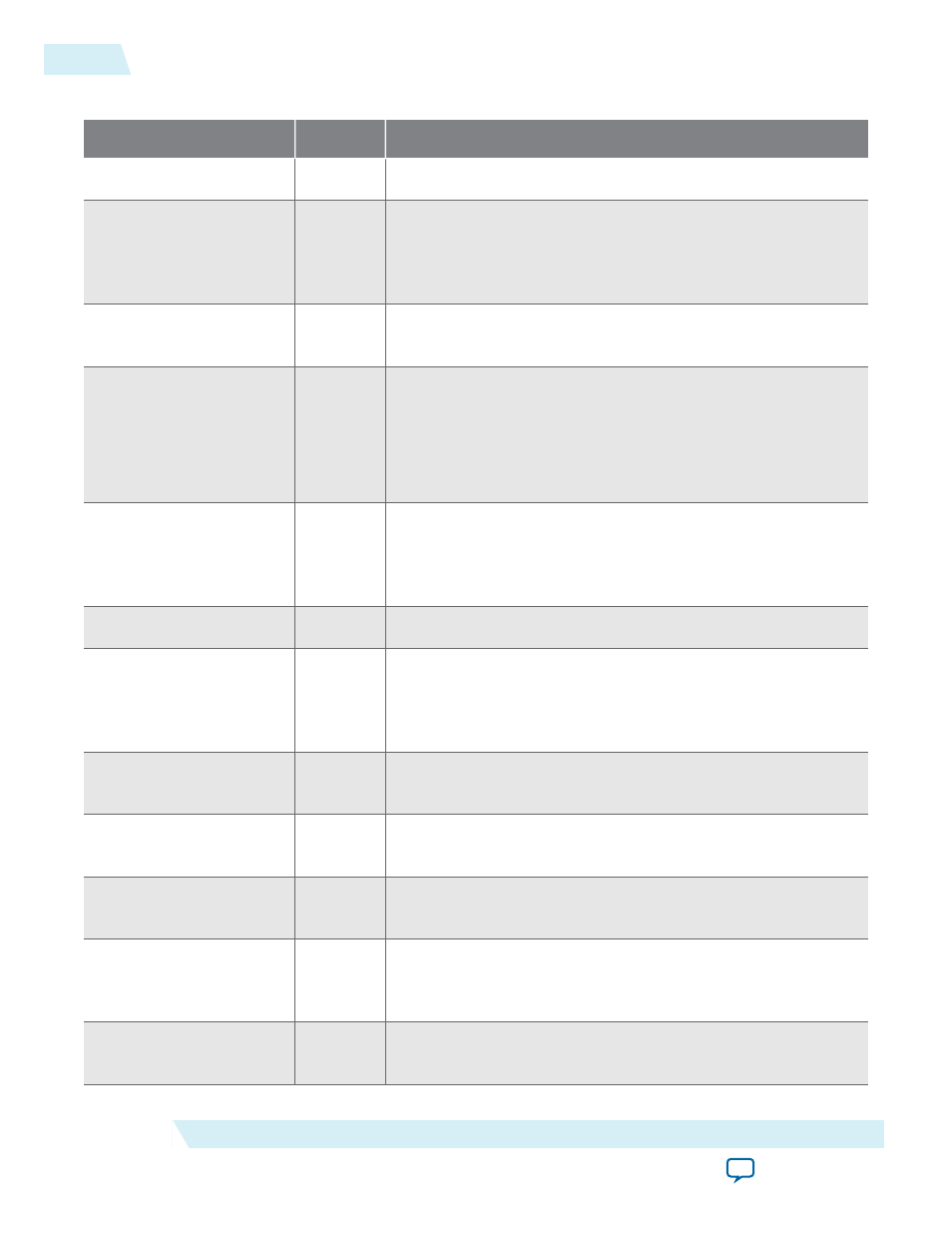

Table 6-22: PIPE Interface Signals

Signal

Direction

Description

txdata0[31:0]

Output

Transmit data

txdatak0[3:0]

Output

Transmit data control

for

txdata

txdata

, and so on. A value of 0 indicates a data byte. A value of 1

indicates a control byte. For Gen1 and Gen2 only.

txblkst0

Output

For Gen3 operation, indicates the start of a block in the transmit

direction.

txdataskip0

Output

For Gen3 operation. Allows the MAC to instruct the TX interface

to ignore the TX data interface for one clock cycle. The following

encodings are defined:

• 1’b0: TX data is invalid

• 1’b1: TX data is valid

tx_deemph0

Output

Transmit de-emphasis selection. The Arria 10 Hard IP for PCI

Express sets the value for this signal based on the indication

received from the other end of the link during the Training

Sequences (TS). You do not need to change this value.

rxdata0[31:0]

(2)

Input

Receive data

rxdatak[3:0]

(2)

Input

Receive data >n>. This bus receives data on lane

corresponds to the lowest-order byte of

rxdata

, and so on. A

value of 0 indicates a data byte. A value of 1 indicates a control

byte. For Gen1 and Gen2 only.

rxblkst0

Input

For Gen3 operation, indicates the start of a block in the receive

direction.

txdetectrx0

Output

Transmit detect receive

start a receive detection operation or to begin loopback.

txelecidle

Output

Transmit electrical idle

electrical idle.

txcompl0

Output

Transmit compliance

disparity to negative in Compliance Mode (negative COM

character).

rxpolarity0

Output

Receive polarity

invert the polarity of the 8B/10B receiver decoding block.

6-58

PIPE Interface Signals

UG-01145_avst

2015.05.04

Altera Corporation

Interfaces and Signal Descriptions