Generating quartus ii synthesis files, Understanding the files generated, Understanding simulation log file generation – Altera Arria 10 Avalon-ST User Manual

Page 23: Generating quartus ii synthesis files -4, Understanding the files generated -4, Understanding simulation log file generation -4

The simulation includes the following stages:

• Link training

• Configuration

• DMA reads and writes

• Root Port to Endpoint memory reads and writes

Disabling Scrambling to Interpret TLPs at the PIPE Interface

1. Go to

.

2. Open altpcietb_bfm_top_rp.v.

3. Locate the assignment for

test_in[2:1]

. Set

test_in[2] = 1

and

test_in[1] = 0

. Changing

test_in[2] = 1

disables data scrambling on the PIPE interface.

4. Save altpcietb_bfm_top_rp.v.

Generating Quartus II Synthesis Files

1. On the Generate menu, select Generate HDL.

2. For Create HDL design files for synthesis, select Verilog.

You can leave the default settings for all other items.

3. Click Generate to generate files for Quartus II synthesis.

4. Click Finish when the generation completes.

Understanding the Files Generated

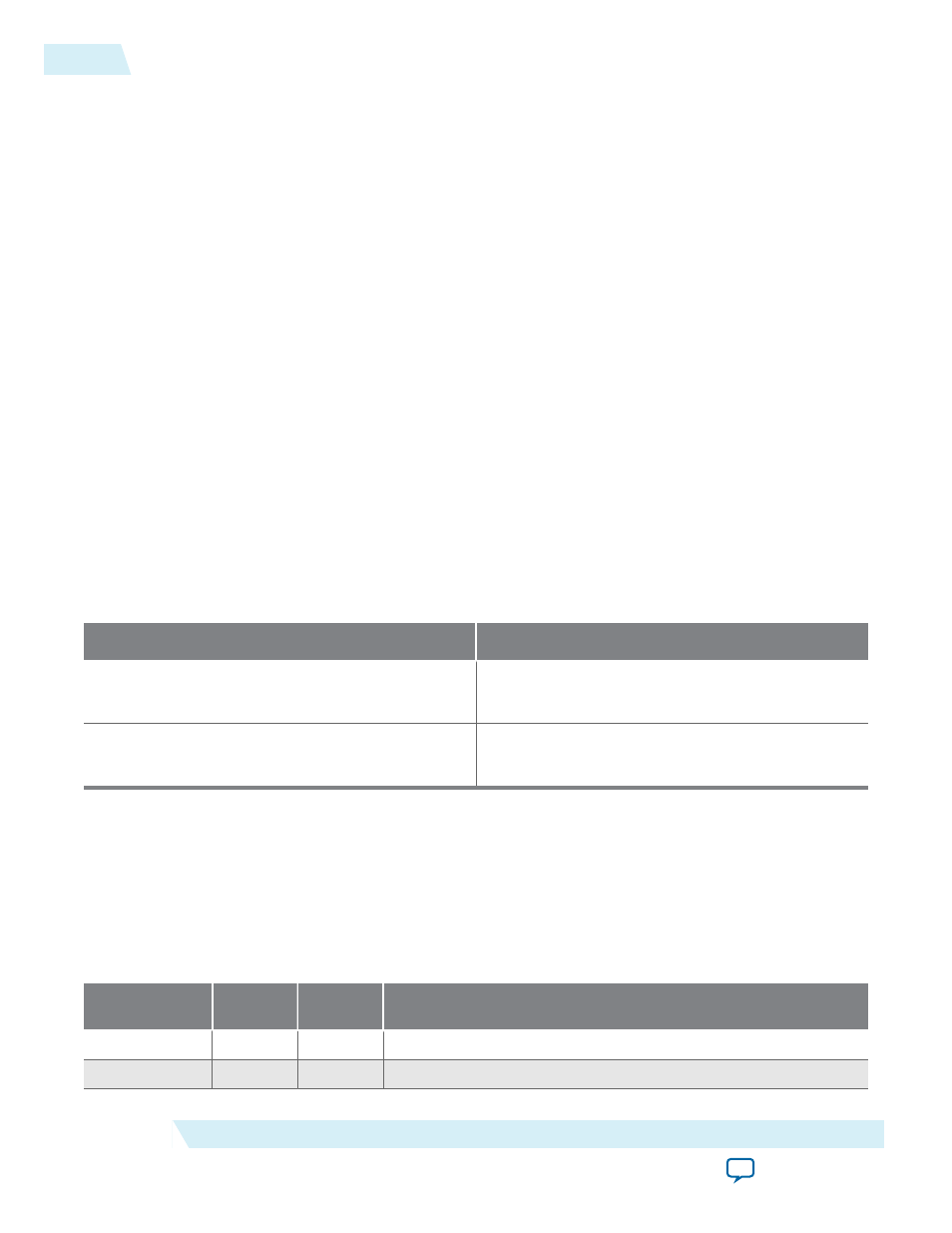

Table 2-2: Overview of Qsys Generation Output Files

Directory

Description

Includes the top-level HDL file for the Hard IP for

PCI Express.

Includes the HDL source files and scripts for the

simulation testbench.

For a more detailed listing of the directories and files the Quartus II software generates, refer to Files

Generated for Altera IP Cores in Compiling the Design in the Qsys Design Flow.

Understanding Simulation Log File Generation

Starting with the Quartus II 14.0 software release, simulation automatically creates a log file,

altpcie_

monitor_

in your simulation directory.

Table 2-3: Sample Simulation Log File Entries

Time

TLP Type

Payload

(Bytes)

TLP Header

17989 RX

CfgRd0

0004

04000001_0000000F_01080008

17989 RX

MRd

0000

00000000_00000000_01080000

2-4

Generating Quartus II Synthesis Files

UG-01145_avst

2015.05.04

Altera Corporation

Getting Started with the Arria 10 Hard IP for PCI Express