Altera Arria 10 Avalon-ST User Manual

Page 86

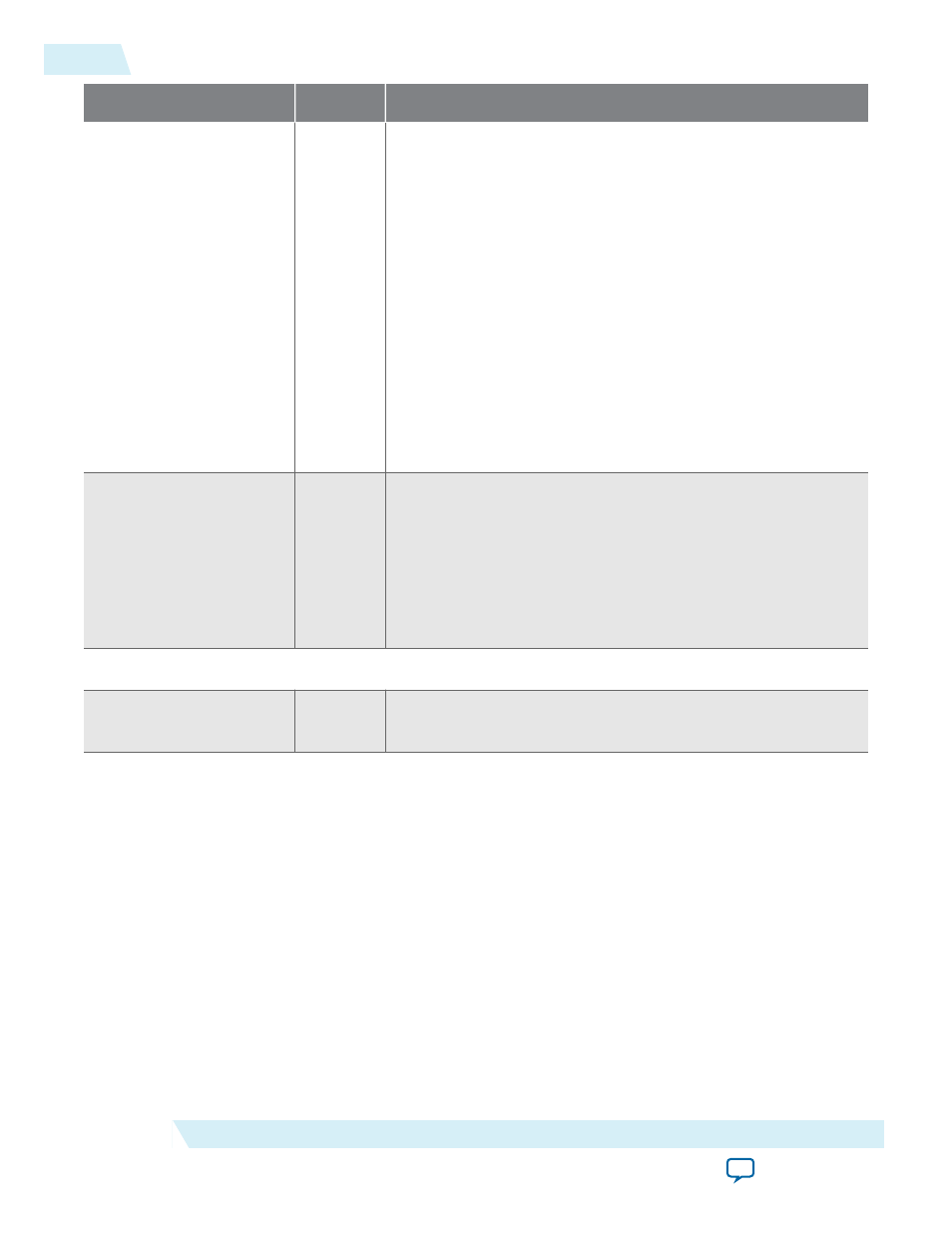

Signal

Direction

Description

tx_st_err

Input

Indicates an error on transmitted TLP. This signal is used to

nullify a packet. It should only be applied to posted and

completion TLPs with payload. To nullify a packet, assert this

signal for 1 cycle after the SOP and before the EOP. When a

packet is nullified, the following packet should not be transmitted

until the next clock cycle.

tx_st_err

is not available for packets

that are 1 or 2 cycles long.

For 256-bit data, when you turn on Enable multiple packets per

cycle, bit 0 applies to the entire bus

tx_st_data[255:0]

. Bit 1 is

not used.

Refer to the figure entitled 128-Bit Avalon-ST tx_st_data Cycle

Definition for 3-Dword Header TLP with non-Qword Aligned

Address for a timing diagram that illustrates the use of the error

signal. Note that it must be asserted while the valid signal is

asserted.

tx_st_parity[

Output

Byte parity is generated when you turn on Enable byte parity

ports on Avalon ST interface on the System Settings tab of the

parameter editor.Each bit represents odd parity of the associated

byte of the

tx_st_data

bus. For example, bit[0] corresponds to

tx_st_data[7:0]

, bit[1] corresponds to

tx_st_data[15:8]

,

and so on.

Component Specific Signals

tx_cred_data_fc[11:0]

Output

Data credit limit for the received FC completions. Each credit is

16 bytes.

6-20

Avalon-ST TX Interface

UG-01145_avst

2015.05.04

Altera Corporation

Interfaces and Signal Descriptions