Altera Arria 10 Avalon-ST User Manual

Page 112

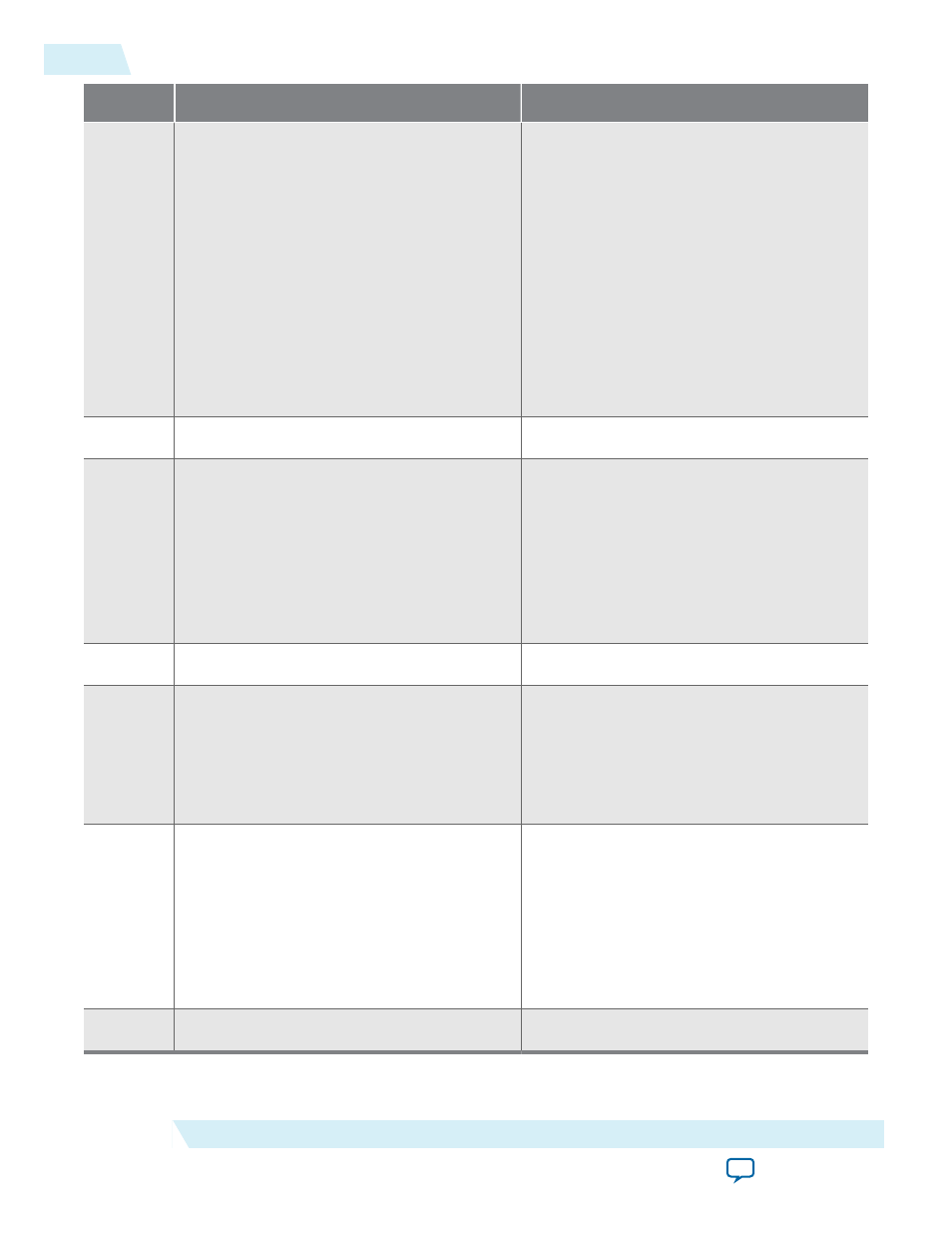

tl_cfg_sts

Configuration Space Register

Description

[46:31] Link Status Register[15:0]

Records the following link status informa‐

tion:

• Bit 15: link autonomous bandwidth status

• Bit 14: link bandwidth management status

• Bit 13: Data Link Layer link active - This

bit is only available for Root Ports. It is

always 0 for Endpoints.

• Bit 12: Slot clock configuration

• Bit 11: Link Training

• Bit 10: Undefined

• Bits[9:4]: Negotiated Link Width

• Bits[3:0] Link Speed

[30]

Link Status 2 Register[0]

Current de-emphasis level.

[29:25] Status Register[15:11]

Records the following 5 primary command

status errors:

• Bit 15: detected parity error

• Bit 14: signaled system error

• Bit 13: received master abort

• Bit 12: received target abort

• Bit 11: signalled target abort

[24]

Secondary Status Register[8]

Master data parity error

[23:6]

Root Status Register[17:0]

Records the following PME status informa‐

tion:

• Bit 17: PME pending

• Bit 16: PME status

• Bits[15:0]: PME request ID[15:0]

[5:1]

Secondary Status Register[15:11]

Records the following 5 secondary command

status errors:

• Bit 15: detected parity error

• Bit 14: received system error

• Bit 13: received master abort

• Bit 12: received target abort

• Bit 11: signalled target abort

[0]

Secondary Status Register[8]

Master Data Parity Error

6-46

Transaction Layer Configuration Space Signals

UG-01145_avst

2015.05.04

Altera Corporation

Interfaces and Signal Descriptions