Interrupts for root ports, Completion side band signals, Interrupts for root ports -38 – Altera Arria 10 Avalon-ST User Manual

Page 104: Completion side band signals -38

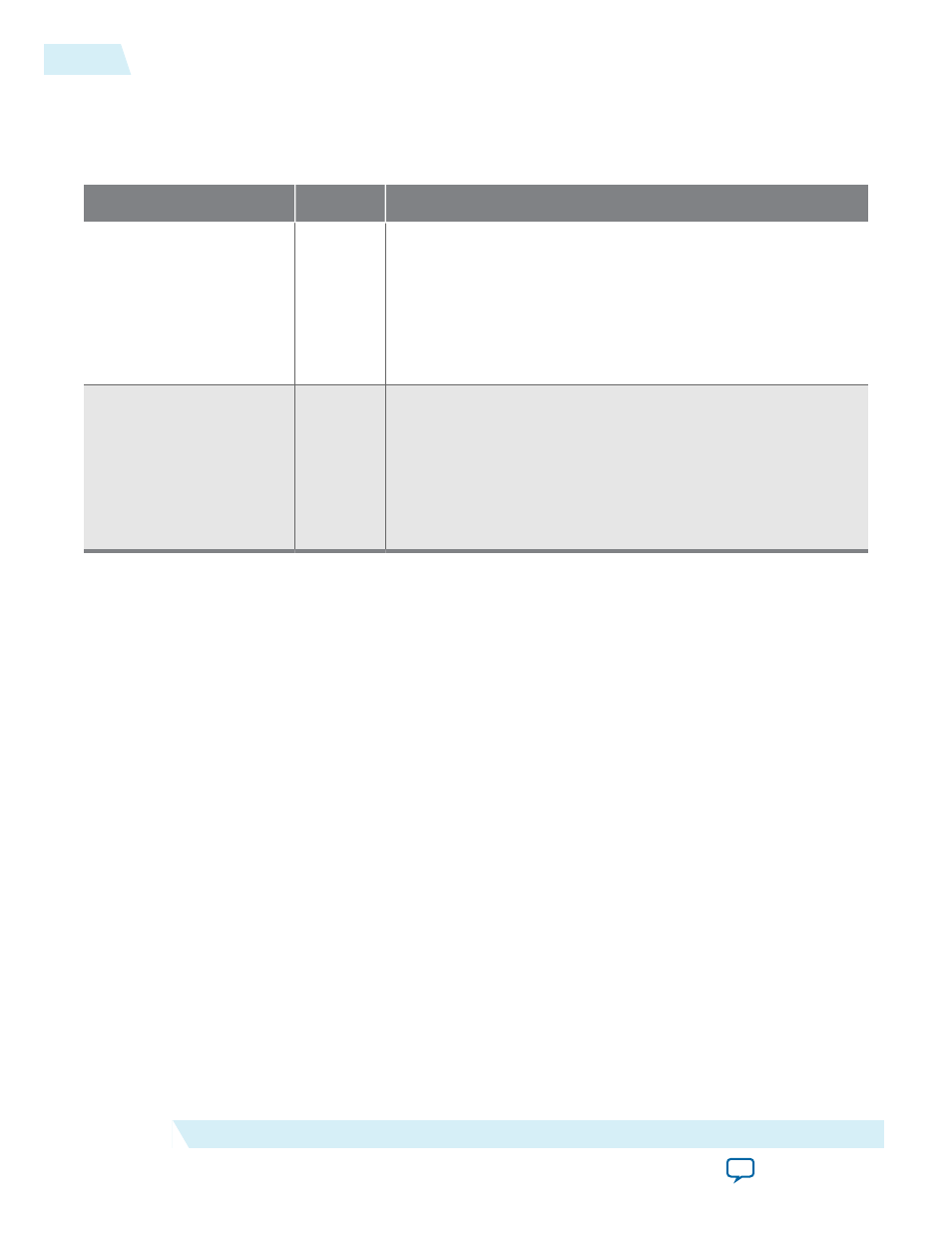

Interrupts for Root Ports

Table 6-10: Interrupt Signals for Root Ports

Signal

Direction

Description

int_status[3:0]

Output

These signals drive legacy interrupts to the Application Layer as

follows:

• int_status[0]: interrupt signal A

• int_status[1]: interrupt signal B

• int_status[2]: interrupt signal C

• int_status[3]: interrupt signal D

serr_out

Output

System Error: This signal only applies to Root Port designs that

report each system error detected, assuming the proper enabling

bits are asserted in the

Root Control

and

Device Control

registers. If enabled,

serr_out

is asserted for a single clock cycle

when a system error occurs. System errors are described in the

PCI Express Base Specification 2.1 or 3.0 in the

Root Control

register.

Related Information

Completion Side Band Signals

The following table describes the signals that comprise the completion side band signals for the Avalon-

ST interface. The Arria 10 Hard IP for PCI Express provides a completion error interface that the

Application Layer can use to report errors, such as programming model errors. When the Application

Layer detects an error, it can assert the appropriate

cpl_err

bit to indicate what kind of error to log. If

separate requests result in two errors, both are logged. The Hard IP sets the appropriate status bits for the

errors in the Configuration Space, and automatically sends error messages in accordance with the PCI

Express Base Specification. Note that the Application Layer is responsible for sending the completion with

the appropriate completion status value for non-posted requests. Refer to Error Handling for information

on errors that are automatically detected and handled by the Hard IP.

For a description of the completion rules, the completion header format, and completion status field

values, refer to Section 2.2.9 of the PCI Express Base Specification.

6-38

Interrupts for Root Ports

UG-01145_avst

2015.05.04

Altera Corporation

Interfaces and Signal Descriptions