Legacy interrupts, Legacy interrupts -6 – Altera Arria 10 Avalon-ST User Manual

Page 155

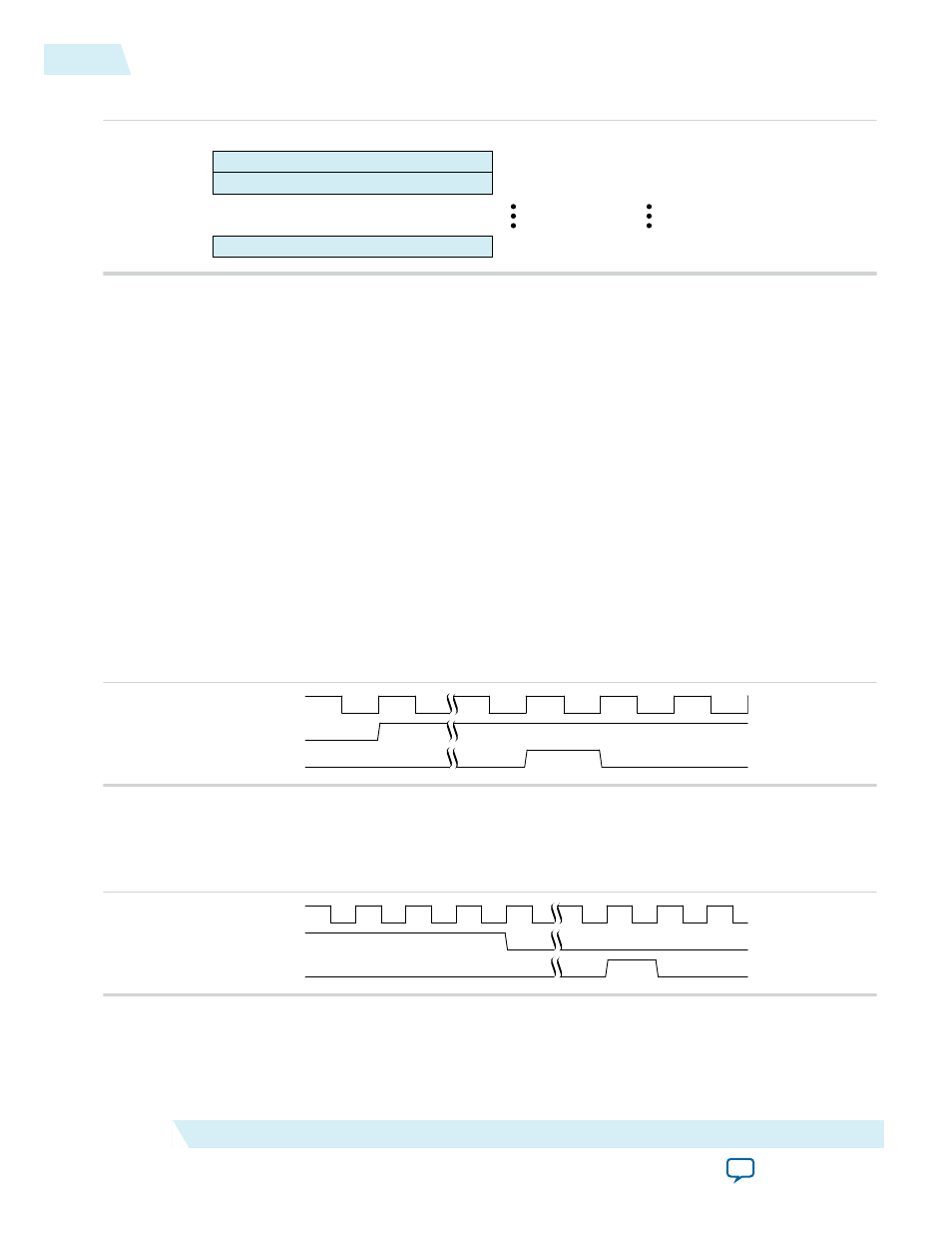

Figure 9-7: MSI-X PBA Table

Pending Bits 0 through 63

Pending Bits 64 through 127

Pending Bits ((N - 1) div 64) × 64 through N - 1

QWORD 0

QWORD 1

QWORD (( N - 1) div 64)

Base

Address

Pending Bit Array (PBA)

Base + 1 × 8

Base + ((N - 1) div 64) × 8

4. The IRQ Processor reads the entry in the MSI-X table.

a. If the interrupt is masked by the

Vector_Control

field of the MSI-X table, the interrupt remains in

the pending state.

b. If the interrupt is not masked, IRQ Processor sends Memory Write Request to the TX slave

interface. It uses the address and data from the MSI-X table. If

Message Upper Address

= 0, the

IRQ Processor creates a three-dword header. If the

Message Upper Address > 0

, it creates a 4-

dword header.

5. The host interrupt service routine detects the TLP as an interrupt and services it.

Related Information

•

•

Legacy Interrupts

The following figure illustrates interrupt timing for the legacy interface. In this figure the assertion of

app_int_sts

instructs the Hard IP for PCI Express to send a

Assert_INTA

message TLP.

Figure 9-8: Legacy Interrupt Assertion

clk

app_int_sts

app_int_ack

The following figure illustrates the timing for deassertion of legacy interrupts. The assertion of

app_int_sts

instructs the Hard IP for PCI Express to send a

Deassert_INTA

message.

Figure 9-9: Legacy Interrupt Deassertion

clk

app_int_sts

app_int_ack

Related Information

Correspondence between Configuration Space Registers and the PCIe Specification

9-6

Legacy Interrupts

UG-01145_avst

2015.05.04

Altera Corporation

Interrupts