Altera Arria 10 Avalon-ST User Manual

Page 10

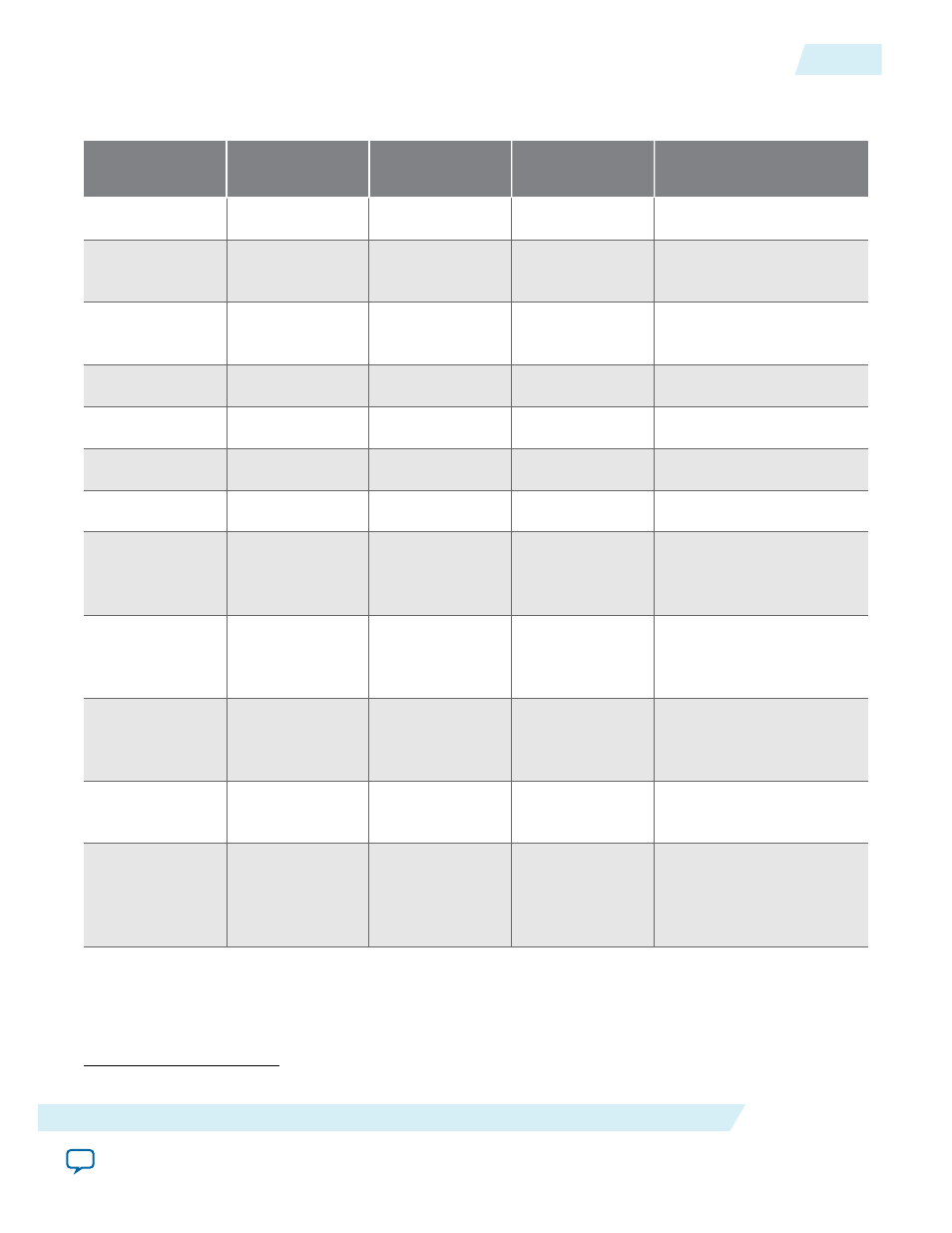

Table 1-2: Feature Comparison for all Hard IP for PCI Express IP Cores

The table compares the features of the four Hard IP for PCI Express IP Cores.

Feature

Avalon-ST Interface

Avalon-MM

Interface

Avalon-MM DMA

Avalon-ST Interface with SR-

IOV

IP Core License Free

Free

Free

Free

Native

Endpoint

Supported

Supported

Supported

Supported

Legacy

Endpoint

(1)

Supported

Not Supported

Not Supported

Not Supported

Root port

Supported

Supported

Not Supported

Not Supported

Gen1

×1, ×2, ×4, ×8

×1, ×2, ×4, ×8

Not Supported

×8

Gen2

×1, ×2, ×4, ×8

×1, ×2, ×4, ×8

×4, ×8

×4, ×8

Gen3

×1, ×2, ×4, ×8

×1, ×2, ×4

×2, ×4, ×8

×2, ×4, ×8

64-bit Applica‐

tion Layer

interface

Supported

Supported

Not supported

Not supported

128-bit

Application

Layer interface

Supported

Supported

Supported

Supported

256-bit

Application

Layer interface

Supported

Not Supported

Supported

Supported

Maximum

payload size

128, 256, 512,

1024, 2048 bytes

128, 256 bytes

128, 256 bytes

128, 256 bytes

Number of tags

supported for

non-posted

requests

256

8

16

256

(1)

Not recommended for new designs.

UG-01145_avst

2015.05.04

Arria 10 Features

1-3

Datasheet

Altera Corporation