3 address tracing enable (ate) - bit 15, 4 patch enable (pen) - bit 23, Address tracing enable (ate) - bit 15 -2 – Freescale Semiconductor DSP56366 User Manual

Page 76: Patch enable (pen) - bit 23 -2, Table 4-1, Operating mode register (omr) -2

Operating Mode Register (OMR)

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

4-2

Freescale Semiconductor

4.2.1

Asynchronous Bus Arbitration Enable (ABE) - Bit 13

The asynchronous bus arbitration mode is activated by setting the ABE bit in the OMR register. Hardware

reset clears the ABE bit.

4.2.2

Address Attribute Priority Disable (APD) - Bit 14

The Address Attribute Priority Disable (APD) bit is used to turn off the address attribute priority

mechanism. When this bit is set, more than one address attribute pin AA/RAS(2:0) may be simultaneously

asserted according to its AAR settings. The APD bit is cleared by hardware reset.

4.2.3

Address Tracing Enable (ATE) - Bit 15

The Address Tracing Enable (ATE) bit is used to turn on Address Tracing (AT) Mode. When the AT Mode

is enabled, the DSP56300 Core reflects the addresses of internal fetches and program space moves

(MOVEM) to the Address Bus (A0-A17), if the Address Bus is not needed by the DSP56300 Core for

external accesses. The ATE bit is cleared on hardware reset.

4.2.4

Patch Enable (PEN) - Bit 23

The Patch Enable function is used for patching Program ROM locations. i.e. to replace during program

execution, the contents of the Program ROM. This is done by using the Instruction Cache to supply the

instruction word instead of the Program ROM.

The Patch Enable function is activated by setting bit 23 (PEN) in the OMR Register. The PEN bit is cleared

by hardware reset.

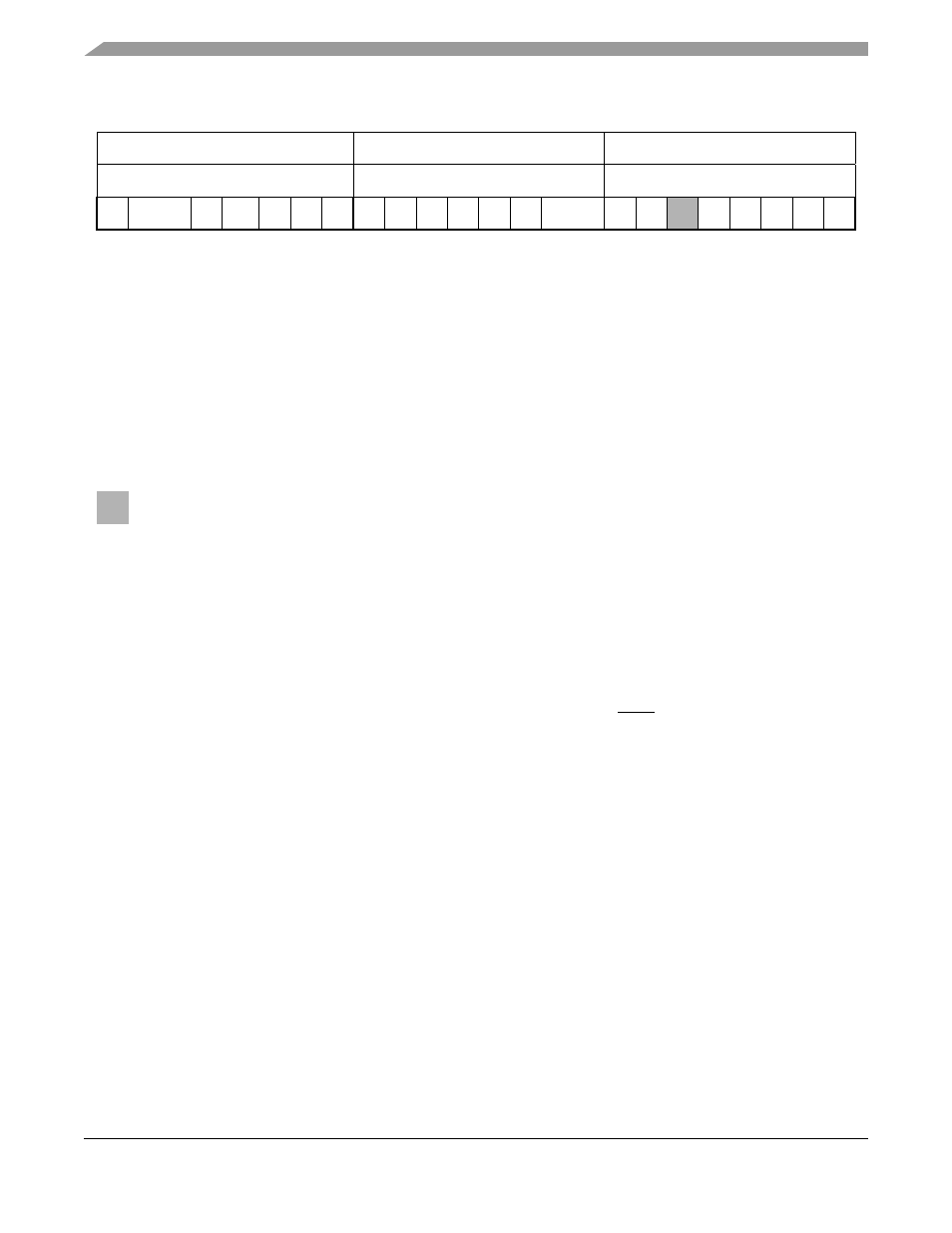

Table 4-1 Operating Mode Register (OMR)

SCS

EOM

COM

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

PEN MSW 1 : 0 SEN WRP EOV EUN XYS ATE APD ABE BRT TAS

BE

CDP1:0

MS

SD

EBD MD

MC

MB

MA

PEN

- Patch Enable

ATE

- Address Tracing Enable

MS

- Master memory Switch Mode

MSW1

- Memory switch mode 1

APD

- Address Priority Disable

SD

- Stop Delay

MSW0

- Memory switch mode 0

ABE

- Asyn. Bus Arbitration Enable

SEN

- Stack Extension Enable

BRT

- Bus Release Timing

EBD

- External Bus Disable

WRP

- Extended Stack Wrap Flag

TAS

- TA Synchronize Select

MD

- Operating Mode D

EOV

- Extended Stack Overflow Flag

BE

- Burst Mode Enable

MC

- Operating Mode C

EUN

- Extended Stack Underflow Flag

CDP1

- Core-Dma Priority 1

MB

- Operating Mode B

XYS

- Stack Extension Space Select

CDP0

- Core-Dma Priority 0

MA

- Operating Mode A

- Reserved bit. Read as zero, should be written with zero for future compatibility