1 shi input/output shift register (iosr)-host side, Table 7-1, Shi interrupt vectors -5 – Freescale Semiconductor DSP56366 User Manual

Page 129: Table 7-2, Shi internal interrupt priorities -5, Below and, Section 7.4.1, "shi input/output shift register, Iosr)—host side, 1 shi input/output shift register (iosr)—host side

Serial Host Interface Programming Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor

7-5

The SHI interrupt vector table is shown in

and the exception priorities generated by the SHI are

shown in

7.4.1

SHI Input/Output Shift Register (IOSR)—Host Side

The variable length Input/Output Shift Register (IOSR) can be viewed as a serial-to-parallel and

parallel-to-serial buffer in the SHI. The IOSR is involved with every data transfer in both directions (read

and write). In compliance with the I

2

C and SPI bus protocols, data is shifted in and out MSB first. In 8-bit

data transfer modes, the most significant byte of the IOSR is used as the shift register. In 16-bit data

transfer modes, the two most significant bytes become the shift register. In 24-bit transfer modes, the shift

register uses all three bytes of the IOSR (see

NOTE

The IOSR cannot be accessed directly either by the host processor or by the

DSP. It is fully controlled by the SHI controller logic.

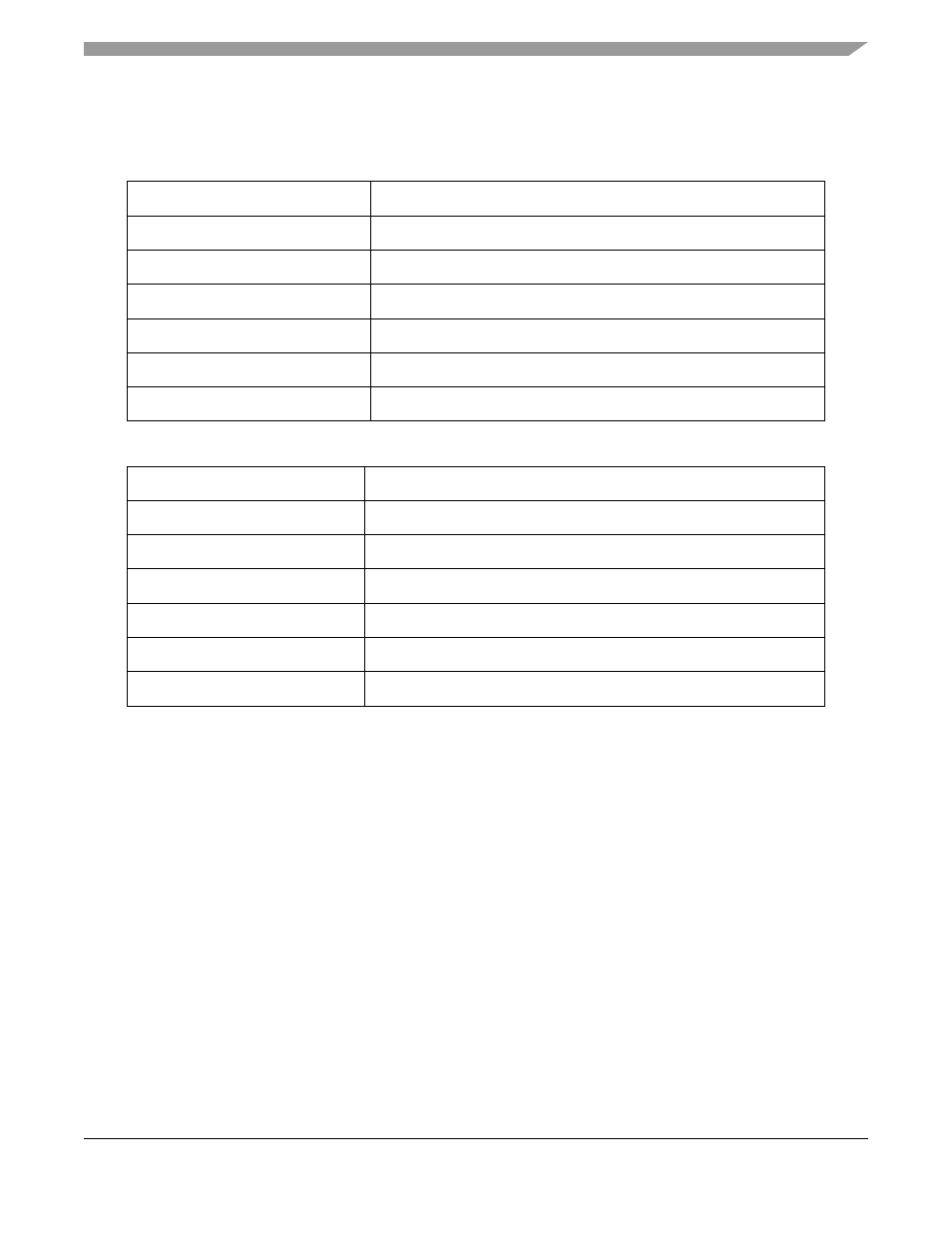

Table 7-1 SHI Interrupt Vectors

Program Address

Interrupt Source

VBA:$0040

SHI Transmit Data

VBA:$0042

SHI Transmit Underrun Error

VBA:$0044

SHI Receive FIFO Not Empty

VBA:$0048

SHI Receive FIFO Full

VBA:$004A

SHI Receive Overrun Error

VBA:$004C

SHI Bus Error

Table 7-2 SHI Internal Interrupt Priorities

Priority

Interrupt

Highest

SHI Bus Error

SHI Receive Overrun Error

SHI Transmit Underrun Error

SHI Receive FIFO Full

SHI Transmit Data

Lowest

SHI Receive FIFO Not Empty