Esai – Freescale Semiconductor DSP56366 User Manual

Page 341

Programming Sheets

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor

D-33

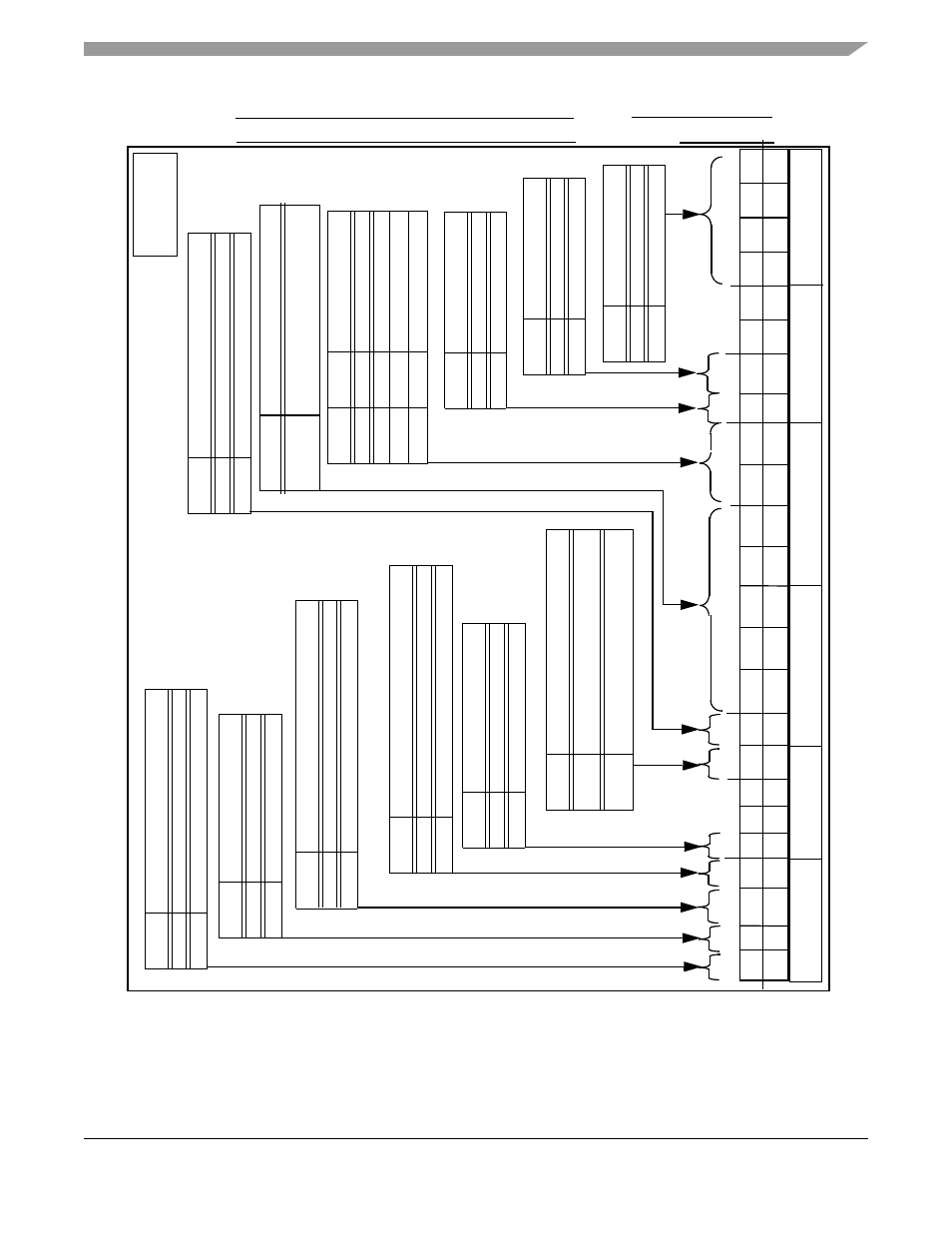

Figure D-18. ESAI Receive Control Register

15

6

5

4

19

18

17

16

10

9

8

7

14

12

13

11

RE0

3

210

RE2

23

22

21

20

RE1

RE3

Rs

vd

R

svd

RS

HF

D

RW

A

RF

SL

RF

SR

RE

IE

RE

DI

E

RIE

RLI

E

R

S

W

S

[

0

:4]

D

escrip

tio

n

Defin

e

s slot and data w

o

rd length

ESAI

RCR - ESAI Receive

Control Register

X: $F

FFFB7 Reset: $000000

See 8.3.4.9

and table 8-8

RS

W

S

4

R

SW

S

3

RSW

S

2

R

SWS1

RSWS0

RM

O

D

0

RM

OD

1

Rsvd

R

svd

RP

R

Application:

Date:

Programmer:

RLIE

Descrip

tio

n

0

R

eceive Last Slot Interr

upt disa

bled

1

R

eceive Last Slot int

errup

t enabled

RIE

D

e

scriptio

n

0

R

eceive I

nterr

upt disabled

1

R

eceive inter

rupt en

abled

REDIE

D

escrip

tio

n

0

R

eceive Even Slot

Data Inter

rupt disable

d

1

R

eceive Even Slot

Data Inter

rupt en

abled

REIE

Descrip

tion

0

R

eceive Exception Inte

rrup

t disabled

1

R

eceive Exception Inte

rrup

t enabled

RPR

D

escrip

tion

0

R

eceiver N

ormal Op

eration

1

R

eceiver Per

son

al R

eset

R

F

SL

Descrip

tion

0

W

o

rd length fr

ame sync

1

1-bit clock p

eriod frame

sync

R

W

A

D

esc

ri

p

tio

n

0

D

ata left aligned

1

D

ata r

igh

t aligned

RE [0:

3]

D

es

cr

ip

tio

n

0

R

eceiver

disabled

1

R

eceiver

enabled

RSHF

D

D

es

cr

ip

tio

n

0

D

ata shifted in MSB fir

st

1

D

ata shifted in LSB fir

st

RMOD1

R

MOD0

Network Mo

de

0

0

Nor

m

al mode

0

1

Net

w

ork mode

10

R

es

er

ve

d

11

A

C

97

RF

SR

Desc

ri

p

tio

n

0

Word-

lengt

h frame

sync synchr

onous to

beginning of data w

ord first slot

1

Word-

lengt

h frame sync 1

clock befor

e

beginning of data w

ord first slot