Figure 7-4, Shi programming model—dsp side -4, Figure 7-4 shi programming model—dsp side – Freescale Semiconductor DSP56366 User Manual

Page 128

Serial Host Interface Programming Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

7-4

Freescale Semiconductor

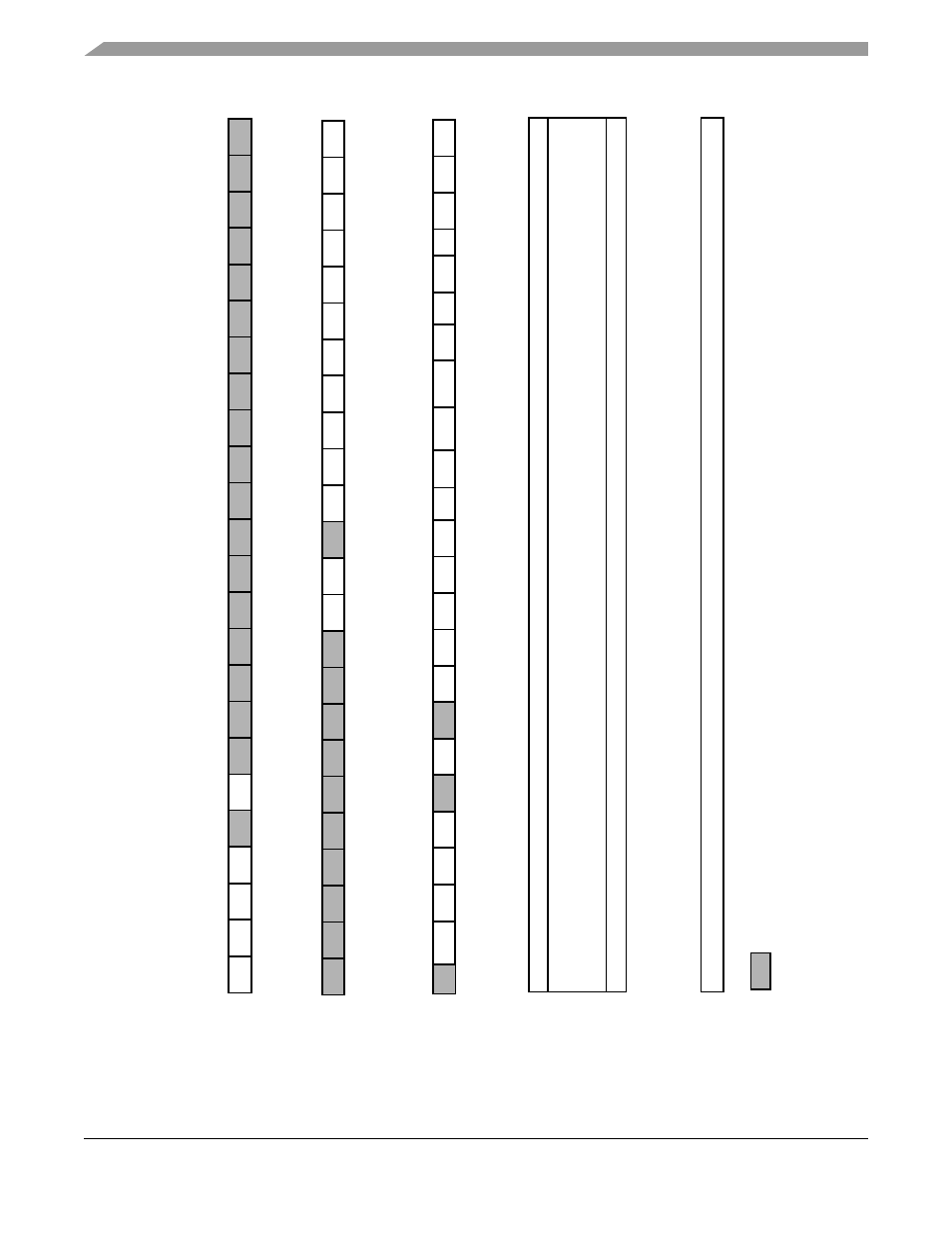

Figure 7-4 SHI Programming Model—DSP Side

HCKFR

8

15

14

1

3

1

2

11

10

9

16

2

3

2

2

21

20

1

9

18

17

0

23

SHI Re

ceive

Data

FI

F

O

(H

RX)

(read only,

X: $FFFF

94)

HR

X

S

H

I Tran

smit

D

a

ta

Registe

r (H

TX

)

(write only,

X: $FFFF

93)

Rese

rve

d

b

it,

re

a

d

as 0

,

sh

ou

ld

be

written

with 0

f

o

r futu

re

co

mp

atib

ility.

HDM

5

HFM1

0

76

5432

1

HD

M6

HD

M

7

HFM0

HDM2

HD

M0

HDM1

HRS

HDM

3

HDM4

CPHA

CPOL

SHI Clo

ck Con

trol

R

e

g

ister

(

HCKR)

X: $FFFF90

0

23

HTX

8

15

14

1

3

1

2

11

10

9

16

2

3

2

2

21

20

1

9

18

17

HE

N

0

76

5

4

3

2

1

HM

1

HI

2

C

HM0

HR

Q

E

0

H

M

S

T

HRNE

HBER

HRFF

HR

O

E

HBUSY

HRQE1

HIDL

E

SHI Co

ntro

l/Sta

tus Re

giste

r (HCSR)

HRIE0

HR

IE

1

HTUE

HTDE

HTIE

X: $FFFF91

FIFO

(10

W

o

rd

s Deep)

HB

IE

HFIFO

8

15

14

1

3

1

2

11

10

9

16

2

3

2

2

21

20

1

9

18

17

HA6

0

76

5432

1

HA3

HA4

HA5

SHI I

2

C

Sl

a

v

e A

ddr

e

ss R

e

g

ist

er

(

H

S

A

R

)

X: $FFFF92

HA1

AA0419