10 rcr receiver frame sync length (rfsl) - bit 15, Rcr receiver frame sync length (rfsl) - bit 15 -30 – Freescale Semiconductor DSP56366 User Manual

Page 180

ESAI Programming Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

8-30

Freescale Semiconductor

8.3.4.10

RCR Receiver Frame Sync Length (RFSL) - Bit 15

The RFSL bit selects the length of the receive frame sync to be generated or recognized. If RFSL is cleared,

a word-length frame sync is selected. If RFSL is set, a 1-bit clock period frame sync is selected. See

for examples of frame length selection.

8.3.4.11

RCR Receiver Frame Sync Relative Timing (RFSR) - Bit 16

RFSR determines the relative timing of the receive frame sync signal as referred to the serial data lines,

for a word length frame sync only. When RFSR is cleared the word length frame sync occurs together with

the first bit of the data word of the first slot. When RFSR is set the word length frame sync starts one serial

clock cycle earlier (i.e. together with the last bit of the previous data word).

8.3.4.12

RCR Receiver Section Personal Reset (RPR) - Bit 19

The RPR control bit is used to put the receiver section of the ESAI in the personal reset state. The

transmitter section is not affected. When RPR is cleared, the receiver section may operate normally. When

RPR is set, the receiver section enters the personal reset state immediately. When in the personal reset

state, the status bits are reset to the same state as after hardware reset.The control bits are not affected by

the personal reset state.The receiver data pins are disconnected while in the personal reset state. Note that

to leave the personal reset state by clearing RPR, the procedure described in

0

1

0

1

1

Reserved

0

1

1

1

0

1

0

0

0

1

1

0

0

1

1

1

0

1

0

0

1

0

1

1

0

1

0

1

1

1

1

1

0

0

1

1

1

0

1

0

1

1

0

1

1

1

1

1

0

0

1

1

1

0

1

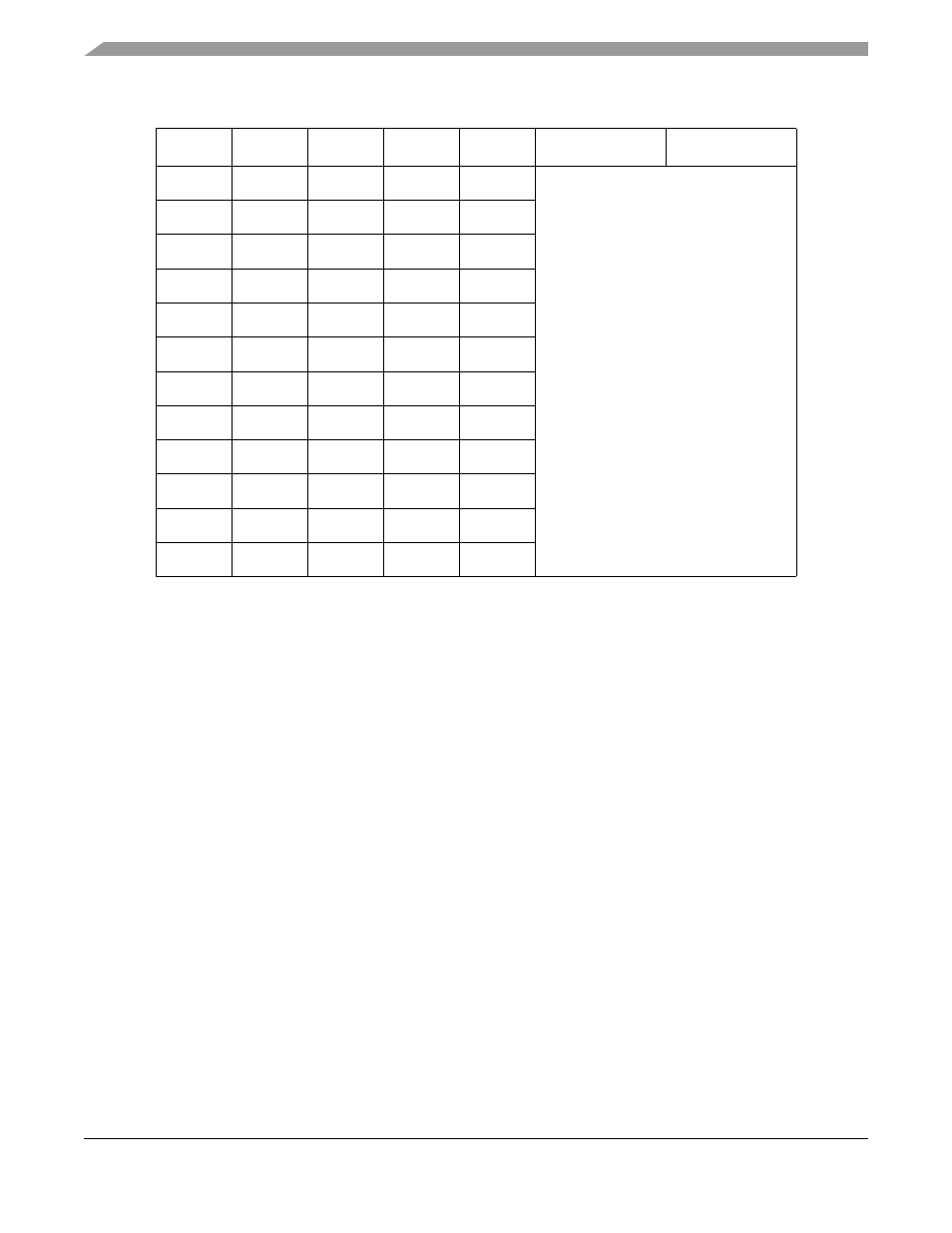

Table 8-11 ESAI Receive Slot and Word Length Selection (continued)

RSWS4

RSWS3

RSWS2

RSWS1

RSWS0

SLOT LENGTH

WORD LENGTH