Esai_1 – Freescale Semiconductor DSP56366 User Manual

Page 345

Programming Sheets

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor

D-37

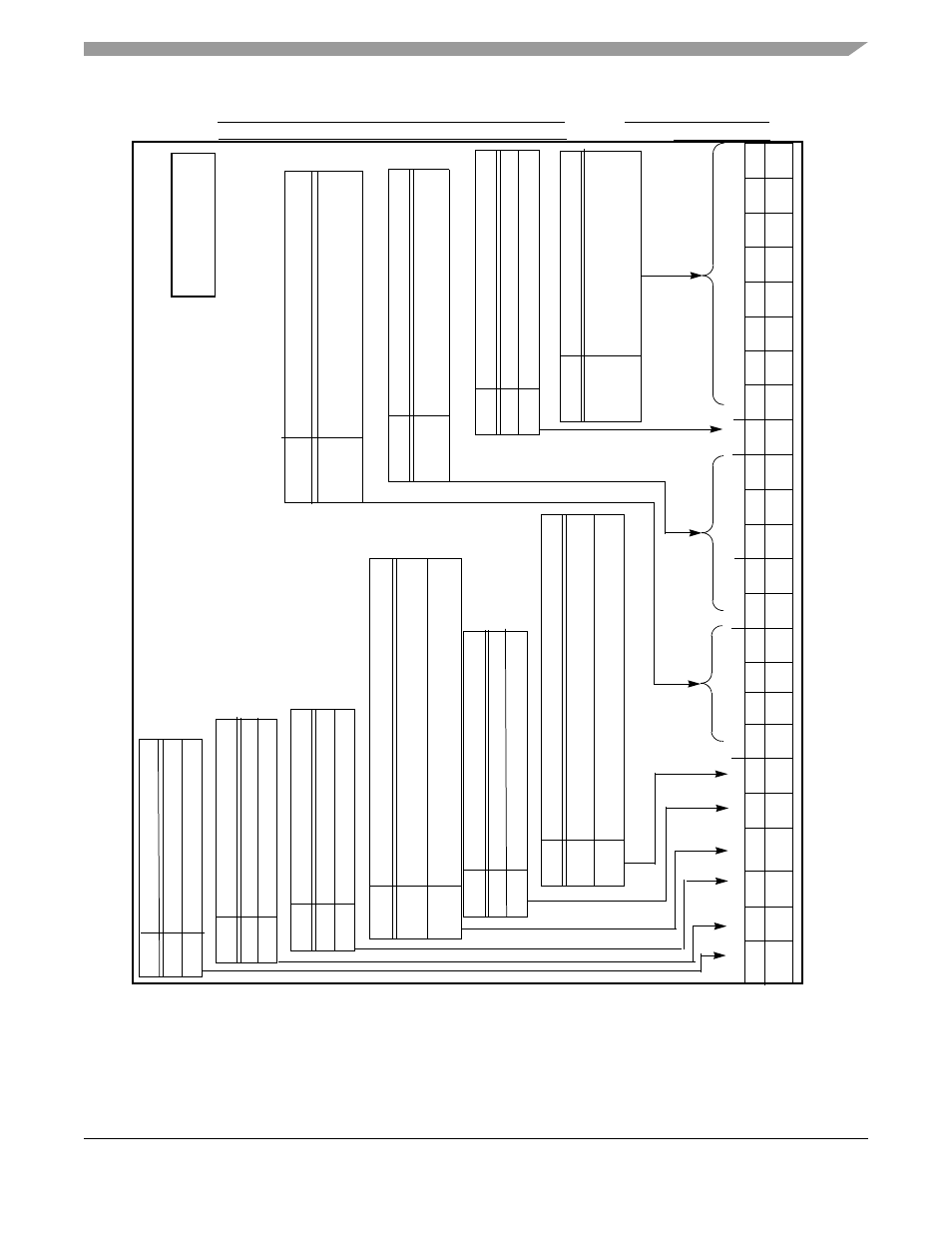

Figure D-22. ESAI_1 Transmit Clock Control Register

Application:

Date:

Programmer:

15

6

5

4

19

18

17

16

10

9

8

7

14

13

12

11

TPM0

32

10

TPM2

23

22

21

20

TP

M

1

TP

M

3

TPM4

TPM5

TP

M

6

TPM7

TP

S

R

TDC0

TDC1

TDC2

TD

C3

TDC4

TF

P

0

TF

P

1

TFP2

TFP3

TCK

P

TFS

P

THCK

P

TCKD

TFSD

THCK

D

TCKP

Descrip

tio

n

0

1

Tr

ansmitter

Clo

ck Pola

rity set to clo

ckout on r

ising edge of

transmit clock, latch in on

falling edge o

f transmit clock.

Tr

ansmitter

Clo

ck Pola

rity set to

clo

ckout on fa

lling e

dge of

T

F

SP

Descrip

tio

n

0

1

Fra

m

e sync polarity po

sitive

Fra

m

e sync polarity ne

gative

TF

P [3:0

]

De

scripti

on

Divider

control.

TCK

D

Descrip

tio

n

0

1

External clock sour

ce

used

Inter

nal clock source

TF

SD

Des

criptio

n

0

1

F

S

T_1 is input

F

S

T_1 is output

THCKD

Des

criptio

n

0

1

Reserved

Must be set for pr

oper

operation

T

HCKP

D

escript

ion

0

1

Keep cleared for

pr

oper

ope

ration

Reserved

Ra

nge $0 -

$F (

1 -16)

.

T

DC [

4:0]

D

e

scripti

on

Divider

contr

ol. Range $00

- $F

F (1

- 32)

TPM [

7:0]

D

e

scripti

on

S

p

ecifie

s the

prescaler

divid

e rate is

tran

smitter clock gener

ator

TPSR

Descript

ion

0

1

Divide b

y 8 pr

escaler op

erational

Divide b

y 8 pr

escaler bypassed

Range fr

om $00 -

$FF (

1 - 2

56).

AA

1777

for the

ESAI_1

TCCR_1 - ESAI_1 Transmit

Clock Control Register

Y: $FFF

F96 Reset: $000000

transmit clock, latch in on ri

sing ed

ge of tran

smit clock