Esai_1 – Freescale Semiconductor DSP56366 User Manual

Page 346

Programming Sheets

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

D-38

Freescale Semiconductor

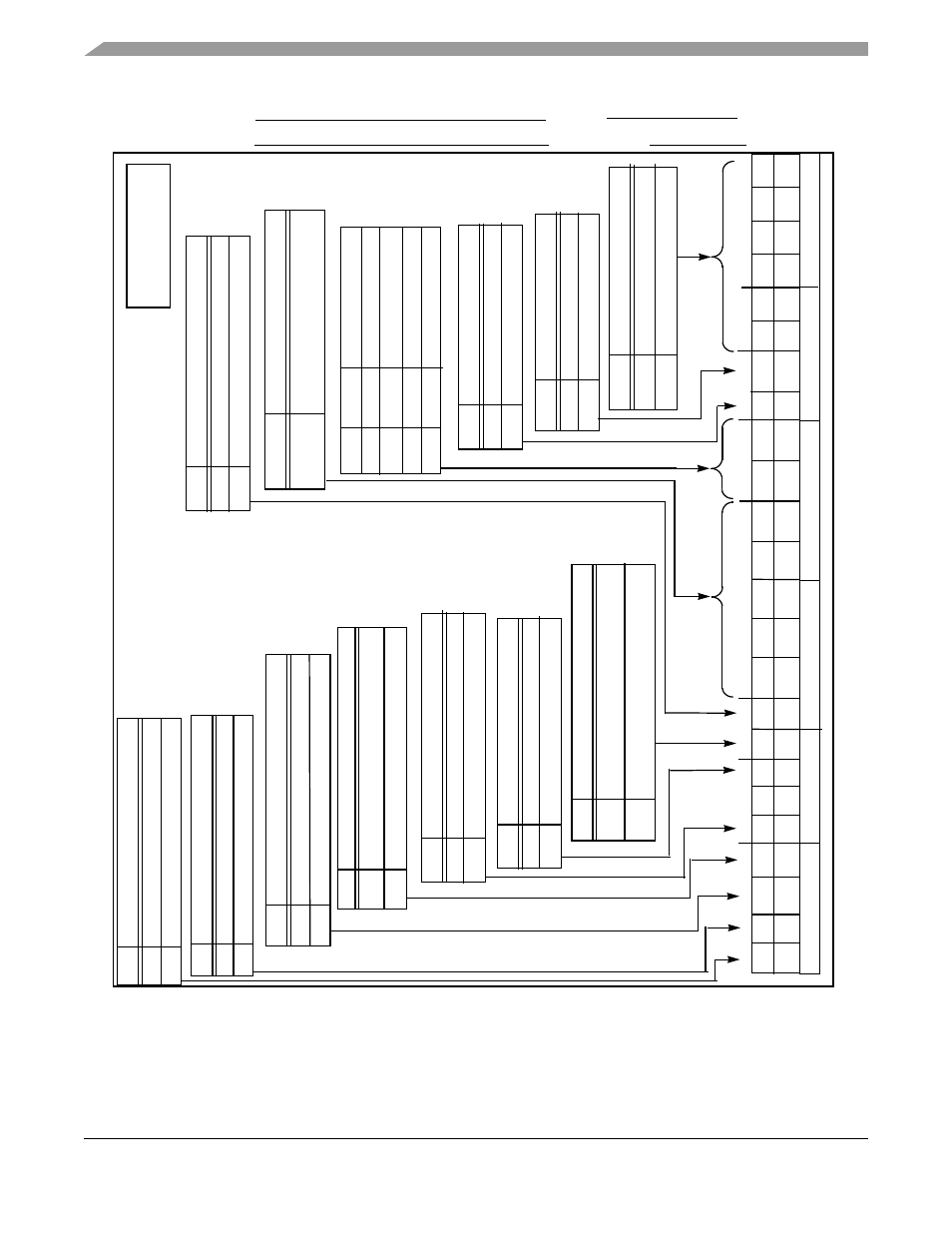

Figure D-23. ESAI_1 Transmit Control Register

15

6

5

4

19

18

17

16

10

9

8

7

14

13

12

11

TE0

3

210

TE

2

23

22

21

20

TE

1

TE

3

TE4

TE5

TSHFD

TMOD0

TFS

L

TF

S

R

TEI

E

TE

D

IE

TIE

TLIE

TF

SR

Descript

ion

0

1

Wor

d-length fr

ame sync synchron

ous to

be

ginning of d

ata word

fir

st slot

Wor

d-length fr

ame sync 1 clock before

be

ginning of d

ata word

fir

st slot

Desc

ri

p

tio

n

TMOD1

N

et

w

ork Mo

de

N

ormal m

ode

T

E

DIE

D

escript

ion

0

1

T

ransmit Even Slot Data Int

errup

t enabled

TIE

Descrip

tio

n

0

1

Tr

ansmit Inte

rrup

t disabled

Tr

ansmit Inte

rrup

t enabled

TL

IE

D

es

c

ri

pt

io

n

0

1

Tra

nsmit Last Slot

Interr

upt disabled

Tra

nsmit Last Slot

Interr

upt enabled

TEIE

Descript

ion

0

1

T

ransmit Exception Inter

rupt disabled

0

TSW

S

[0:4

]

D

e

scripti

on

D

efine

s slo

t and data w

ord length

TF

SL

Descrip

tio

n

0

1

TCR_1 - ESAI_1 T

ransm

it Control Register

Y: $FFFF95 Reset: $000000

TW

A

D

escript

ion

0

1

Data left align

ed

Data r

ight a

ligned

TSHF

D

D

escript

ion

0

1

Data shifted out MSB first

Data shifted out LSB first

TE [

0:5]

Tr

ansmitter

disabled

Tr

ansmitter

enabled

D

escript

ion

0

1

Word length fr

ame sync

1-bit clock period fra

m

e sync

Tr

ansmitter

Nor

m

al Oper

ation

T

ransmit Exception Inter

rupt ena

bled

Tr

ansmit Even Slot

Data Inter

rupt disable

d

TWA

TM

O

D

1

TSWS4

TS

WS

3

T

SW

S2

TSW

S

1

TSWS0

TMOD0

0

0

0

1

Ne

two

rk m

ode

Re

se

rv

ed

AC

97

1

1

1

PA

D

C

TP

R

Tr

ansmitter

P

e

rsonal R

ese

t

0

1

D

escript

ion

Z

ero Pad

ding d

isabled

PADC

Z

ero Padding enab

led

0

1

TP

R

Application:

Date:

Programmer:

*

0

ESAI_1