5 dax internal architecture, Dax internal architecture -4, Figure 10-2 – Freescale Semiconductor DSP56366 User Manual

Page 220: Dax programming model -4, Table 10-1, Dax interrupt vectors -4, Table 10-2, Dax interrupt priority -4, Accessible dax registers are shown in, The registers are described in the

DAX Internal Architecture

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

10-4

Freescale Semiconductor

10.5

DAX Internal Architecture

are described in the following sections. The DAX

programming model is illustrated in

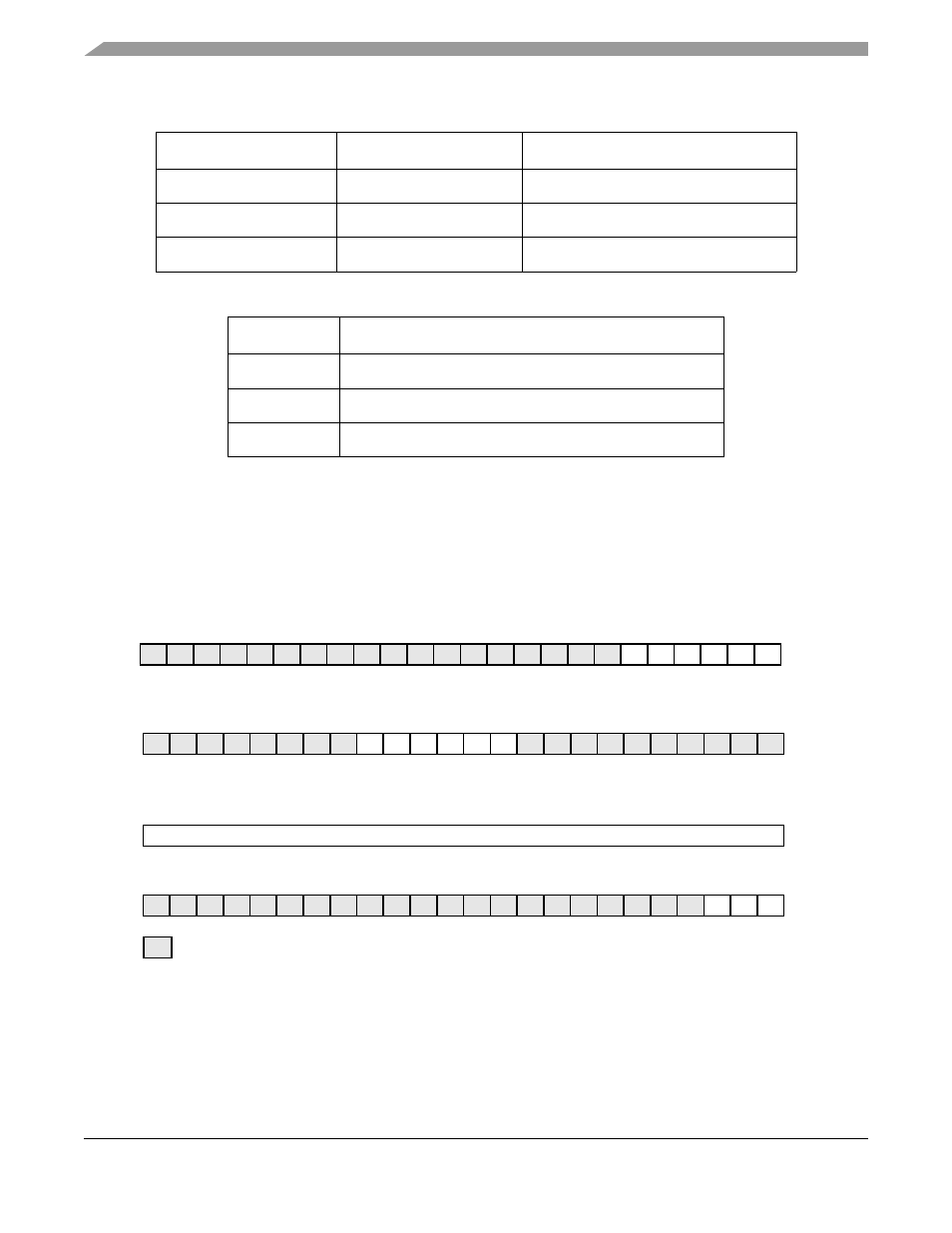

Figure 10-2 DAX Programming Model

Table 10-1 DAX Interrupt Vectors

Condition

Address

Description

XAUR

VBA:$28

DAX transmit underrun error

XADE & XBLK

VBA:$2A

DAX block transferred

XADE

VBA:$2E

DAX audio data register empty

Table 10-2 DAX Interrupt Priority

Priority

Interrupt

highest

DAX transmit underrun error

DAX block transferred

lowest

DAX audio data register empty

23

1

2

21

22

8

XBLK

3

4

7

9

18

17

16

19

20

XADE

0

6

5

13

12

11

10

14

15

Reserved bit

0

23

1

2

21

22

8

3

6

5

7

9

XVA

10

XCB

15

XUB

14

XVB

13

XCA

12

XUA

11

18

17

16

19

20

4

0

23

XAUR

XADRA - Audio Data Register A - X:$FFFFD2 and XADRB - Audio Data Register B -X:$FFFFD3

XNADR - Non-Audio Data Register - X:$FFFFD1

XSTR - Status Register - X:$FFFFD4

0

23

1

2

21

22

8

XCS0

3

6

5

7

9

10

15

14

13

12

11

18

17

16

19

20

XCS1

4

XUIE

XSB

XBIE

XDIE

XCTR - Control Register - X:$FFFFD0