4 esai_1 receive clock control register (rccr_1), Esai_1 receive clock control register (rccr_1) -9, Figure 9-7 – Freescale Semiconductor DSP56366 User Manual

Page 209: Rccr_1 register -9, Table 9-3, Receiver clock sources (asynchronous mode only) -9

ESAI_1 Programming Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor

9-9

9.3.4

ESAI_1 Receive Clock Control Register (RCCR_1)

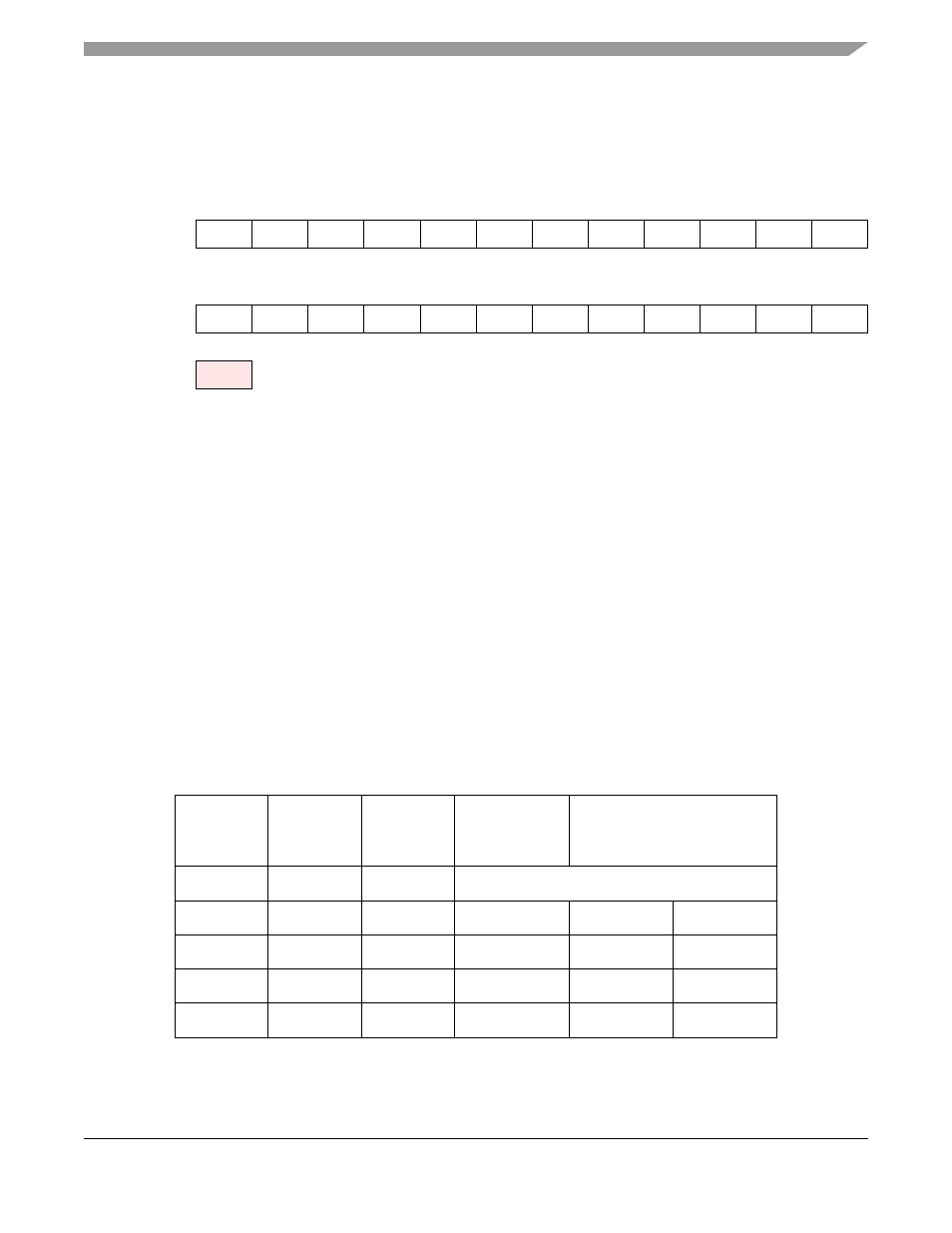

The read/write Receive Clock Control Register (RCCR_1) controls the ESAI_1 receiver clock generator

bit and frame sync rates, word length, and number of words per frame for the serial data.

Hardware and software reset clear all the bits of the RCCR_1 register.

9.3.4.1

RCCR_1 Rx High Freq. Clock Divider (RFP3-RFP0) - Bits 14–17

Since the ESAI_1 does not have the receiver high frequency clock pin, the RFP3–RFP0 bits simply specify

an additional division ratio in the clock divider chain. See

.

9.3.4.2

RCCR_1 Rx High Freq. Clock Polarity (RHCKP) - Bit 20

The ESAI_1 does not have the receiver high frequency clock pin. It it recommended that RHCKP should

be kept cleared.

9.3.4.3

RCCR_1 Rx High Freq. Clock Direction (RHCKD) - Bit 23

The ESAI_1 does not have the receiver high frequency clock pin. RHCKD must be set for proper ESAI_1

receiver section operation.

11

10

9

8

7

6

5

4

3

2

1

0

Y:$FFFF98

RDC2

RDC1

RDC0

RPSR

RPM7

RPM6

RPM5

RPM4

RPM3

RPM2

RPM1

RPM0

23

22

21

20

19

18

17

16

15

14

13

12

RHCKD RFSD

RCKD RHCKP RFSP

RCKP

RFP3

RFP2

RFP1

RFP0

RDC4

RDC3

Reserved bit - read as zero; should be written with zero for future compatibility.

Figure 9-7 RCCR_1 Register

Table 9-3 Receiver Clock Sources (asynchronous mode only)

RHCKD

RFSD

RCKD

Receiver

Bit Clock

Source

OUTPUTS

0

X

X

Reserved

1

0

0

SCKR_1

1

0

1

INT

SCKR_1

1

1

0

SCKR_1

FSR_1

1

1

1

INT

FSR_1

SCKR_1