1 esai transmitter clock control register (tccr), Esai transmitter clock control register (tccr) -8, Figure 8-2 – Freescale Semiconductor DSP56366 User Manual

Page 158: Tccr register -8

ESAI Programming Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

8-8

Freescale Semiconductor

special-purpose time slot register.

The following paragraphs give detailed descriptions and operations of

each bit in the ESAI registers.

The ESAI pins can also function as GPIO pins (Port C), described in

.

8.3.1

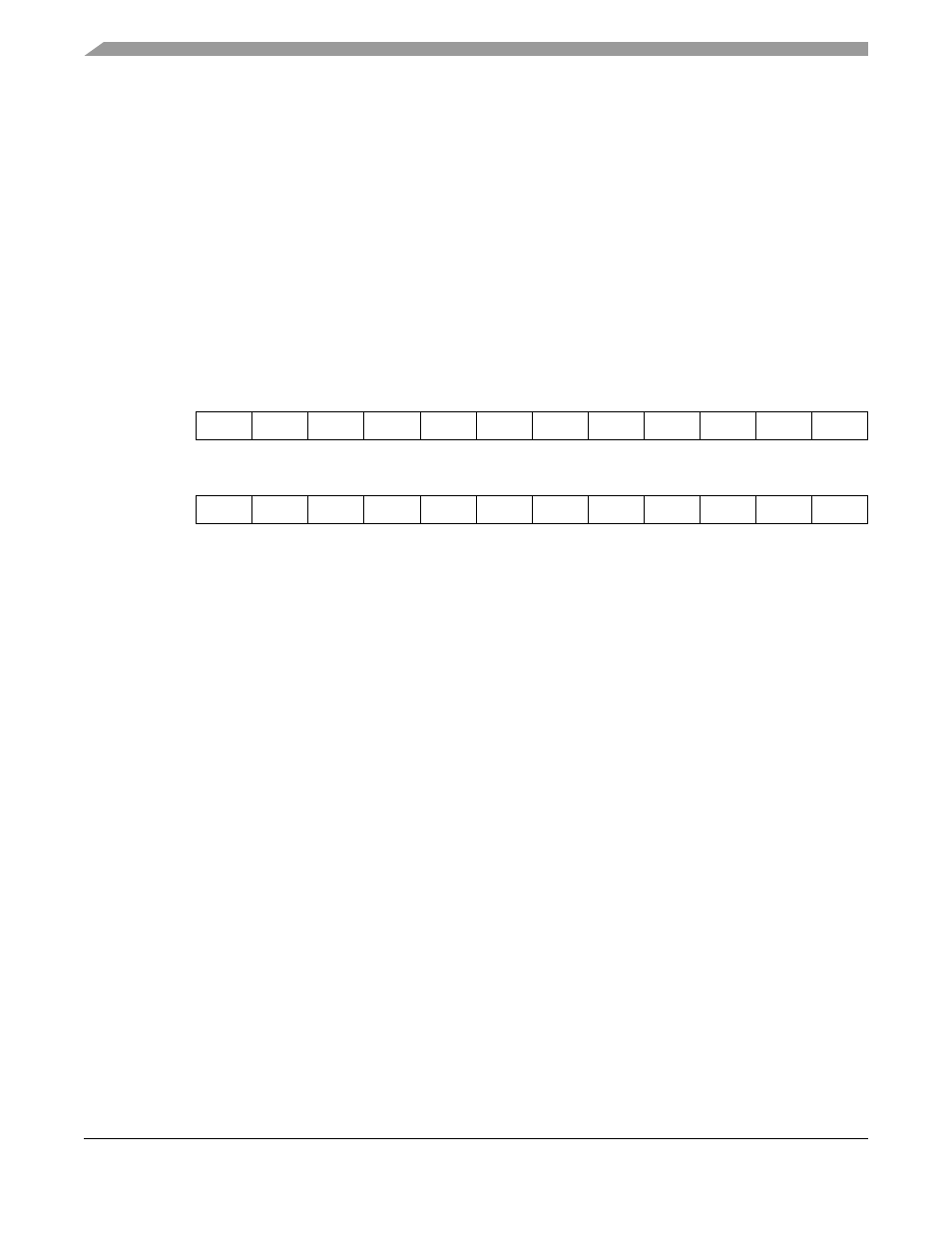

ESAI Transmitter Clock Control Register (TCCR)

The read/write Transmitter Clock Control Register (TCCR) controls the ESAI transmitter clock generator

bit and frame sync rates, the bit clock and high frequency clock sources and the directions of the HCKT,

FST and SCKT signals. (See

). In the synchronous mode (SYN=1), the bit clock defined for the

transmitter determines the receiver bit clock as well. TCCR also controls the number of words per frame

for the serial data.

Hardware and software reset clear all the bits of the TCCR register.

The TCCR control bits are described in the following paragraphs.

8.3.1.1

TCCR Transmit Prescale Modulus Select (TPM7–TPM0) - Bits 0–7

The TPM7–TPM0 bits specify the divide ratio of the prescale divider in the ESAI transmitter clock

generator. A divide ratio from 1 to 256 (TPM[7:0]=$00 to $FF) may be selected. The bit clock output is

available at the transmit serial bit clock (SCKT) pin of the DSP. The bit clock output is also available

internally for use as the bit clock to shift the transmit and receive shift registers. The ESAI transmit clock

generator functional diagram is shown in

.

11

10

9

8

7

6

5

4

3

2

1

0

X:$FFFFB6

TDC2

TDC1

TDC0

TPSR

TPM7

TPM6

TPM5

TPM4

TPM3

TPM2

TPM1

TPM0

23

22

21

20

19

18

17

16

15

14

13

12

THCKD

TFSD

TCKD

THCKP

TFSP

TCKP

TFP3

TFP2

TFP1

TFP0

TDC4

TDC3

Figure 8-2 TCCR Register