Freescale Semiconductor DSP56366 User Manual

Page 335

Programming Sheets

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor

D-27

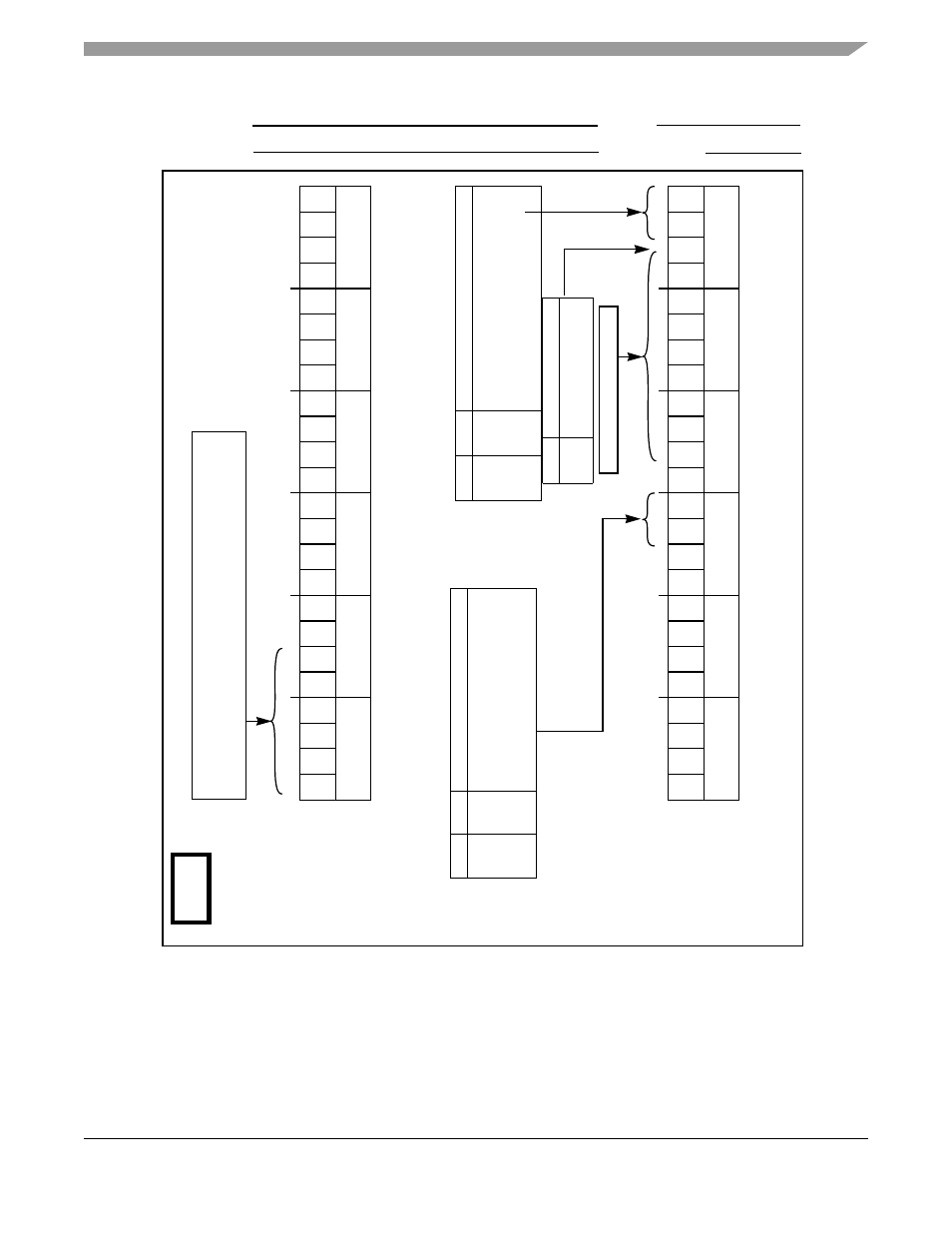

Figure D-12. SHI Slave Address and Clock Control Registers

10

Application:

Date:

Programmer:

Sheet 1 of 3

SHI

15

14

13

12

1

1

9876543210

HDM4

HDM2

HDM

1

HDM0

H

R

S

CPO

LC

P

HA

SHI Clock

Cont

rol

X:

$FF

FF90

Re

set

= $0

00

001

R

e

gister (HCK

R)

19

18

17

16

23

22

21

20

*

0

*

0

HDM3

*

0

HDM7

*

0

*

0

*

0

*

0

15

14

13

12

1

1

1

0

9876543210

SH

I Slave

Addr

ess

X:

$FF

FF92

Res

e

t =

$Bx0

000

Reg

ist

er (

H

SA

R)

19

18

17

16

23

22

21

20

HA1

HA3

HA5

*

0

*

0

HA

6

*

0

*

0

*

0

*

0

*

0

*

0

*

0

*

0

*

0

*

0

*

0

*

0

*

0

*

0

*

0

*

0

*

0

HA

4

0

0

0

0

*

0

*

0

*

0

*

0

00

HDM5

HCKR Divider

Modulu

s

HS

AR

I

2

C Slav

e Add

ress

Slave add

ress

= Bits HA6-HA3,

HA1

and

external pins H

A

2

, HA0

Slave address after reset = 1011[HA2]0[H

A

0]

HF

M1

HFM0

SHI

Noise

Redu

ctio

n F

ilter Mod

e

0

0

Bypasse

d (Filter disabled)

01

R

e

s

e

rv

e

d

1

0

N

a

rrow

spike tolerance

1

1

Wide sp

ike tolerance

HFM0

HFM1

SH

I C

lock C

o

ntrol

Register

(HC

KR)

SHI Slav

e Addre

ss Regis

ter

(

H

SAR)

CPOL

CPHA

R

esult

0

0

SCK active low, strobe on

rising edge

0

1

SCK active low, strobe

on falling edge

1

0

SCK active high, strobe

on falling edge

1

1

SCK active high, strobe on

rising edge

HRS

Resu

lt

0

P

resca

ler operational

1

P

rescaler bypassed

HD

M6

*

= Reserved

, write as 0