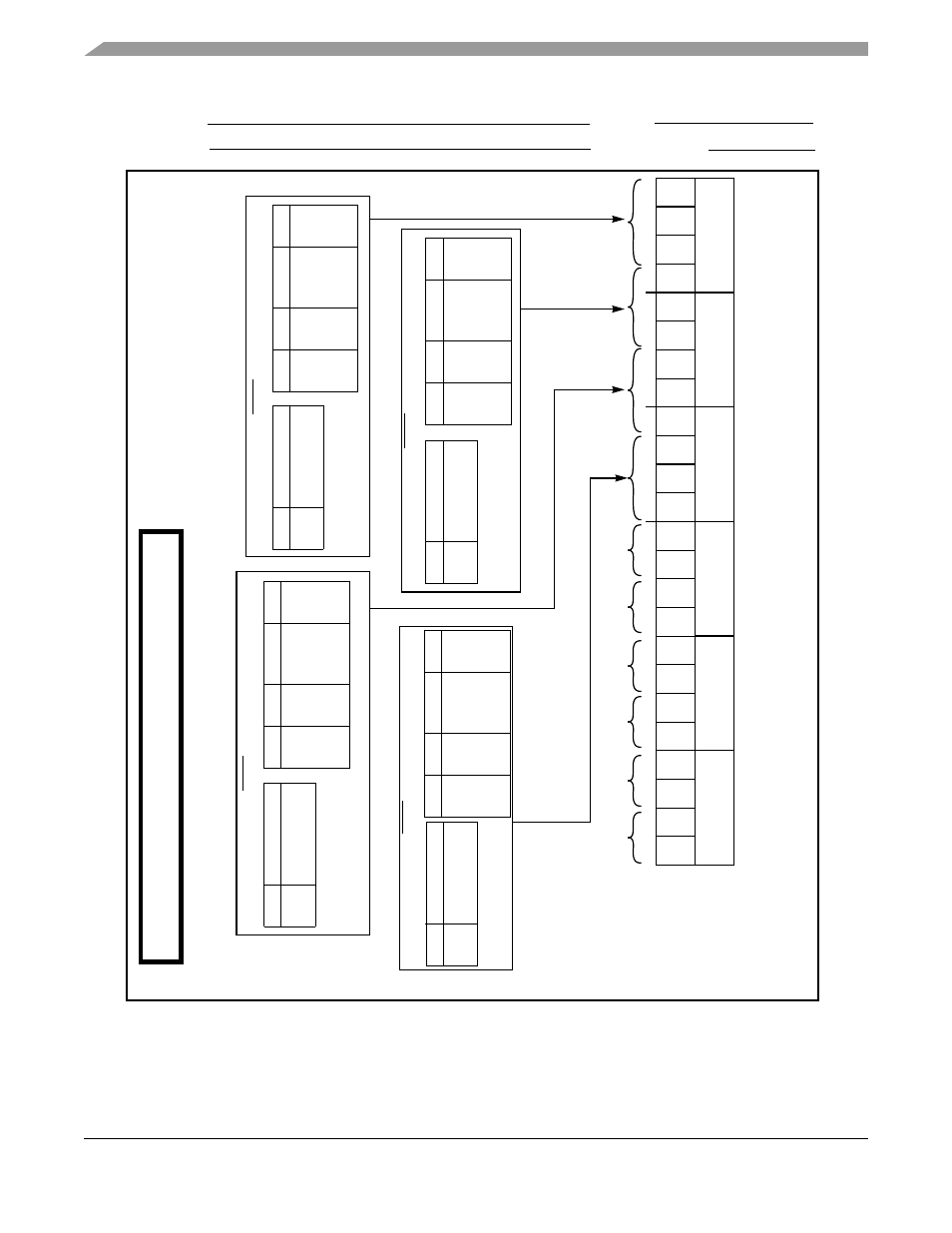

Figure d-3, Central processor – Freescale Semiconductor DSP56366 User Manual

Page 326

Programming Sheets

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

D-18

Freescale Semiconductor

Figure D-3. Interrupt Priority Register–Core (IPR–C)

Application:

Date:

Programmer:

Sheet 3 of 5

CENTRAL PROCESSOR

15

14

13

12

1

1

1

0

9

876543210

D1L0

IDL

2

ID

L1

IB

L2

IB

L1

IBL

0

IA

L2

IA

L1

IA

L0

In

terru

pt Pr

iori

ty

X:

$FFF

FFF

R/

W

D0L1

D0L0

Reset = $000000

Register (IPR–C)

23

22

21

20

19

18

16

17

D1L1

IA

L2

Tri

g

ge

r

0

Level

1

N

eg

. Edge

IR

QA

Mode

IAL

1

IAL

0

Enab

led

IPL

00

N

o

—

01

Y

e

s

0

10

Y

e

s

1

11

Y

e

s

2

IBL

2

Trigg

e

r

0

Level

1

N

eg. Edge

IR

Q

B

M

ode

IBL1

IBL0

Enab

led

IP

L

00

N

o

—

01

Y

e

s

0

10

Y

e

s

1

11

Y

e

s

2

ICL

0

ICL

1

IC

L2

IDL

0

D2

L0

D2L1

D3L0

D3L1

D4L0

D4L1

D5L0

D5

L1

ICL2

T

rigg

e

r

0

Leve

l

1

N

eg.

E

d

ge

IRQ

C

Mode

ICL

1

ICL

0

En

abled

IPL

00

N

o

—

01

Y

e

s

0

10

Y

e

s

1

11

Y

e

s

2

ID

L2

Tri

g

ge

r

0

Level

1

N

eg

. Edge

IR

Q

D

Mod

e

IDL

1

IDL

0

En

abled

IPL

00

N

o

—

01

Y

e

s

0

10

Y

e

s

1

11

Y

e

s

2