Freescale Semiconductor DSP56366 User Manual

Page 315

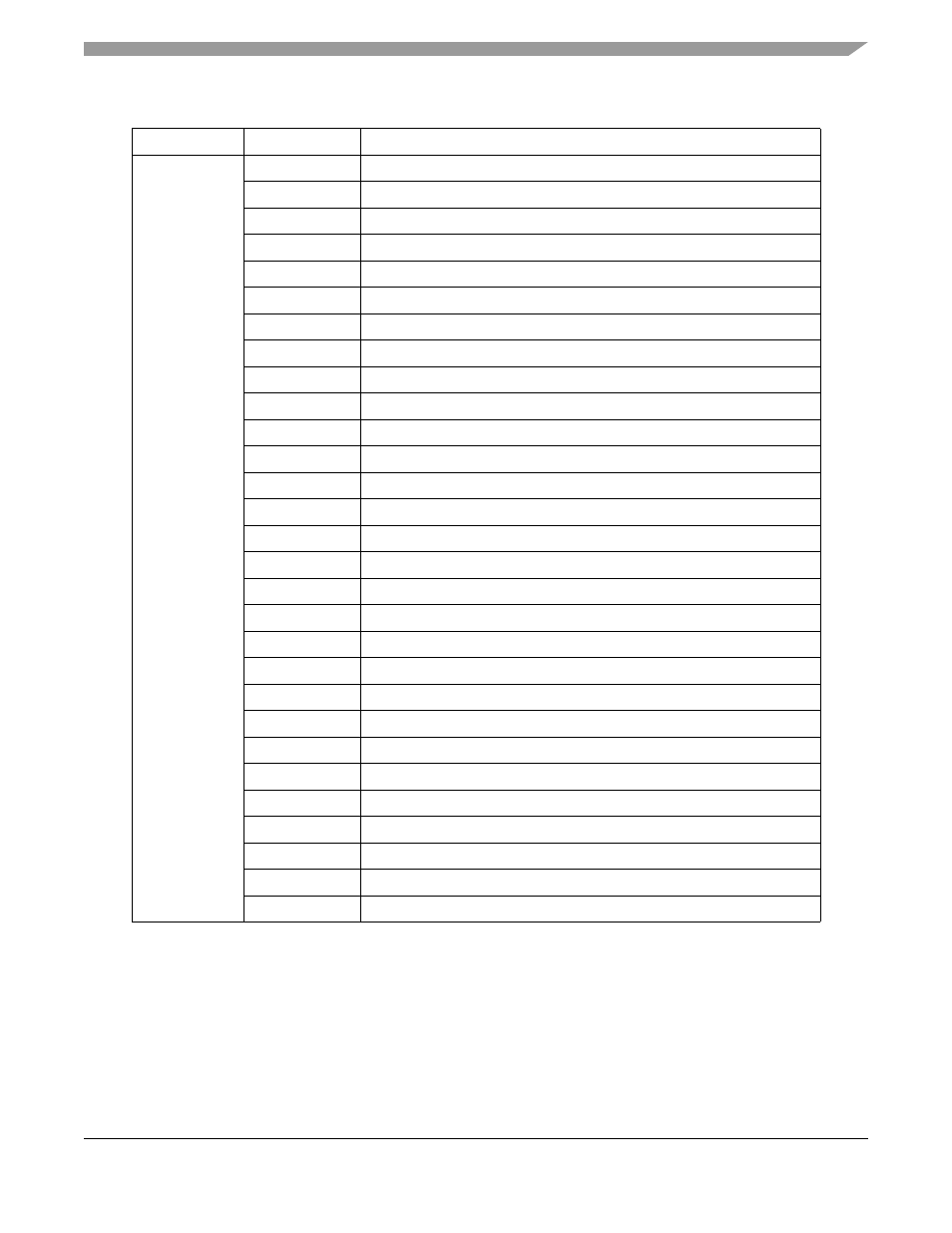

Internal I/O Memory Map

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor

D-7

ESAI_1

Y:$FFFF9C

ESAI_1 RECEIVE SLOT MASK REGISTER B (RSMB_1)

Y:$FFFF9B

ESAI_1 RECEIVE SLOT MASK REGISTER A (RSMA_1)

Y:$FFFF9A

ESAI_1 TRANSMIT SLOT MASK REGISTER B (TSMB_1)

Y:$FFFF99

ESAI_1 TRANSMIT SLOT MASK REGISTER A (TSMA_1)

Y:$FFFF98

ESAI_1 RECEIVE CLOCK CONTROL REGISTER (RCCR_1)

Y:$FFFF97

ESAI_1 RECEIVE CONTROL REGISTER (RCR_1)

Y:$FFFF96

ESAI_1 TRANSMIT CLOCK CONTROL REGISTER (TCCR_1)

Y:$FFFF95

ESAI_1 TRANSMIT CONTROL REGISTER (TCR_1)

Y:$FFFF94

ESAI_1 COMMON CONTROL REGISTER (SAICR_1)

Y:$FFFF93

ESAI_1 STATUS REGISTER (SAISR_1)

Y:$FFFF92

Reserved

Y:$FFFF91

Reserved

Y:$FFFF90

Reserved

Y:$FFFF8F

Reserved

Y:$FFFF8E

Reserved

Y:$FFFF8D

Reserved

Y:$FFFF8C

Reserved

Y:$FFFF8B

ESAI_1 RECEIVE DATA REGISTER 3 (RX3_1)

Y:$FFFF8A

ESAI_1 RECEIVE DATA REGISTER 2 (RX2_1)

Y:$FFFF89

ESAI_1 RECEIVE DATA REGISTER 1 (RX1_1)

Y:$FFFF88

ESAI_1 RECEIVE DATA REGISTER 0 (RX0_1)

Y:$FFFF87

Reserved

Y:$FFFF86

ESAI_1 TIME SLOT REGISTER (TSR_1)

Y:$FFFF85

ESAI_1 TRANSMIT DATA REGISTER 5 (TX5_1)

Y:$FFFF84

ESAI_1 TRANSMIT DATA REGISTER 4 (TX4_1)

Y:$FFFF83

ESAI_1 TRANSMIT DATA REGISTER 3 (TX3_1)

Y:$FFFF82

ESAI_1 TRANSMIT DATA REGISTER 2 (TX2_1)

Y:$FFFF81

ESAI_1 TRANSMIT DATA REGISTER 1 (TX1_1)

Y:$FFFF80

ESAI_1 TRANSMIT DATA REGISTER 0 (TX0_1)

Table D-1. Internal I/O Memory Map (continued)

Peripheral

Address

Register Name