Freescale Semiconductor DSP56366 User Manual

Page 322

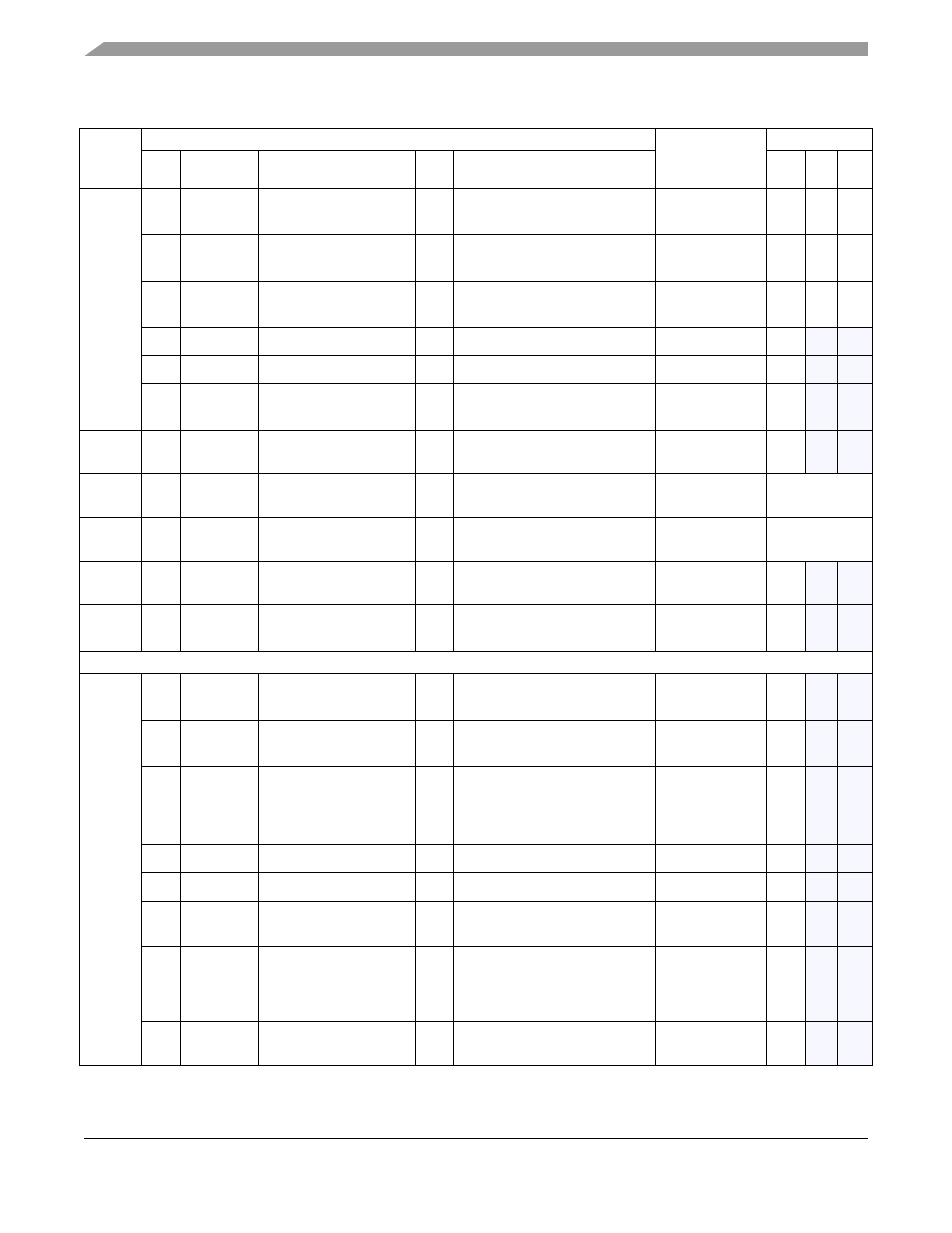

Host Interface—Quick Reference

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

D-14

Freescale Semiconductor

HSR

0

HRDF

Host Receive Data Full

0

1

no receive data to be read

receive data register is full

0

0

0

1

HTDE

Host Transmit Data Empty

1

0

transmit data register empty

transmit data reg. not empty

1

1

1

2

HCP

Host Command Pending

0

1

no host command pending

host command pending

0

0

0

3

HF0

Host Flag0

0

-

-

4

HF1

Host Flag1

0

-

-

7

DMA

DMA Status

0

1

DMA mode disabled

DMA mode enabled

0

-

-

HBAR

7-0

BA10-BA3

Host base Address

Register

$80

HORX

23-0

DSP Receive Data

Register

empty

HOTX

23-0

DSP Transmit Data

Register

empty

HDR

15-0

D15-D0

GPIO Pin Data

$000

0

-

-

HDDR

15-0

DR15-DR0

GPIO Pin Direction

0

1

Input

Output

$000

0

-

-

Host Side

ICR

0

RREQ

Receive Request Enable

0

1

HRRQ interrupt disabled

HRRQ interrupt enabled

0

-

-

1

TREQ

Transmit Request Enable

0

1

HTRQ interrupt disabled

HTRQ interrupt enabled

0

-

-

2

HDRQ

Double Host Request

0

1

HOREQ/HTRQ=HOREQ,

HACK/HRRQ=HACK

HOREQ/HTRQ=HTRQ,

HACK/HRRQ=HRRQ

available if

HDM2-HDM0=000

0

-

-

3

HF0

Host Flag 0

0

-

-

4

HF1

Host Flag 1

0

-

-

5

HLEND

Host Little Endian

0

1

“Big Endian” order

“Little Endian” order

available if

HDM2-HDM0=000

0

-

-

6-5

HM1-HM0

Host Mode Control

00

01

10

11

Interrupt Mode

24-bit DMA enabled

16-bit DMA enabled

8-bit DMA enabled

available if

HDM2-HDM0=100

00

-

-

7

INIT

Initialize

1

Reset data paths according to

TREQ and RREQ

cleared by HDI08

hardware

0

-

-

Table D-4. HDI08 Programming Model (continued)

Reg

Bit

Comments

Reset Type

Num

Mnemonic

Name

Val

Function

HW /

SW

IR

ST