Figure d-1, Central processor – Freescale Semiconductor DSP56366 User Manual

Page 324

Programming Sheets

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

D-16

Freescale Semiconductor

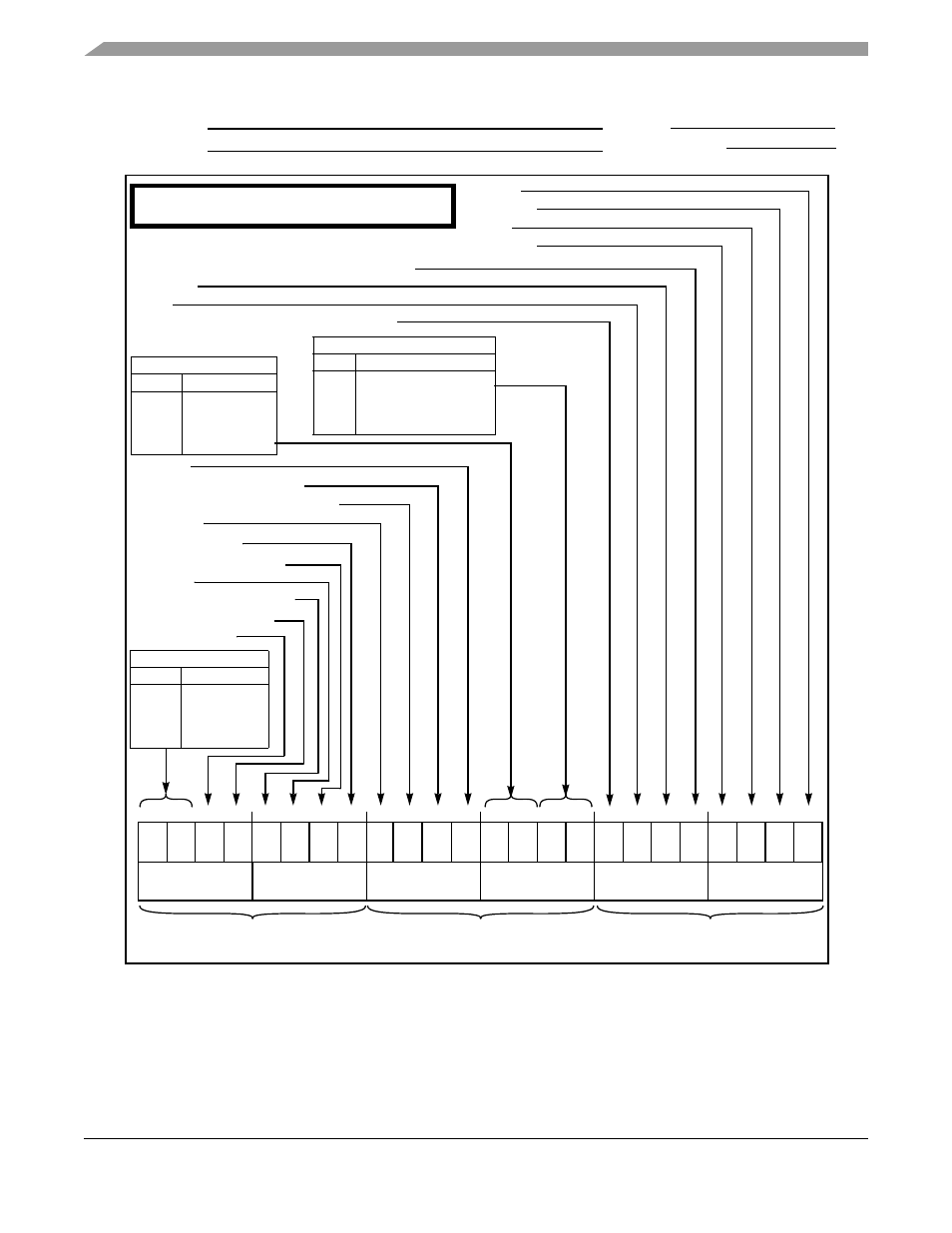

Figure D-1. Status Register (SR)

Application:

Date:

Programmer

:

Sheet 1 of 5

Central Processor

15 14 13 12

11 10

9

8

7

6

5

4

3

2

1

0

U

Z

V

C

19 18 17 16

23 22

21 20

L

LF

S1

SM

I1

I0

CE

SA

FV

S0

N

Scaling Mode

S(1:0)

Scaling Mode

00

01

10

11

No scaling

Scale down

Scale up

Reserved

*

0

*

0

Interrupt Mask

I(1:0)

Exceptions Masked

00

01

10

11

None

IPL 0

IPL 0, 1

IPL 0, 1, 2

Carry

Overfow

Zero

Negative

Unnormalized ( U = Acc(47) xnor Acc(46) )

Extension

Limit

FFT Scaling ( S = Acc(46) xor Acc(45) )

Reserved

Sixteen-Bit Compatibilitity

Double Precision Multiply Mode

Loop Flag

DO-Forever Flag

Sixteenth-Bit Arithmetic

Reserved

Instruction

Cache

Enable

Arithmetic

Saturation

Rounding

Mode

Core Priority

CP(1:0) Core Priority

00

01

10

11

0 (lowest)

1

2

3 (highest)

*

= Reserved, Program as 0

Mode Register (MR)

Condition Code Register (CCR)

Extended Mode Register (MR)

Status Register (SR)

Read/Write

Reset = $C00300

CP1 CP0 RM

DM

SC

S

E