Figure d-9, Host (hdi08), Processor side – Freescale Semiconductor DSP56366 User Manual

Page 332

Programming Sheets

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

D-24

Freescale Semiconductor

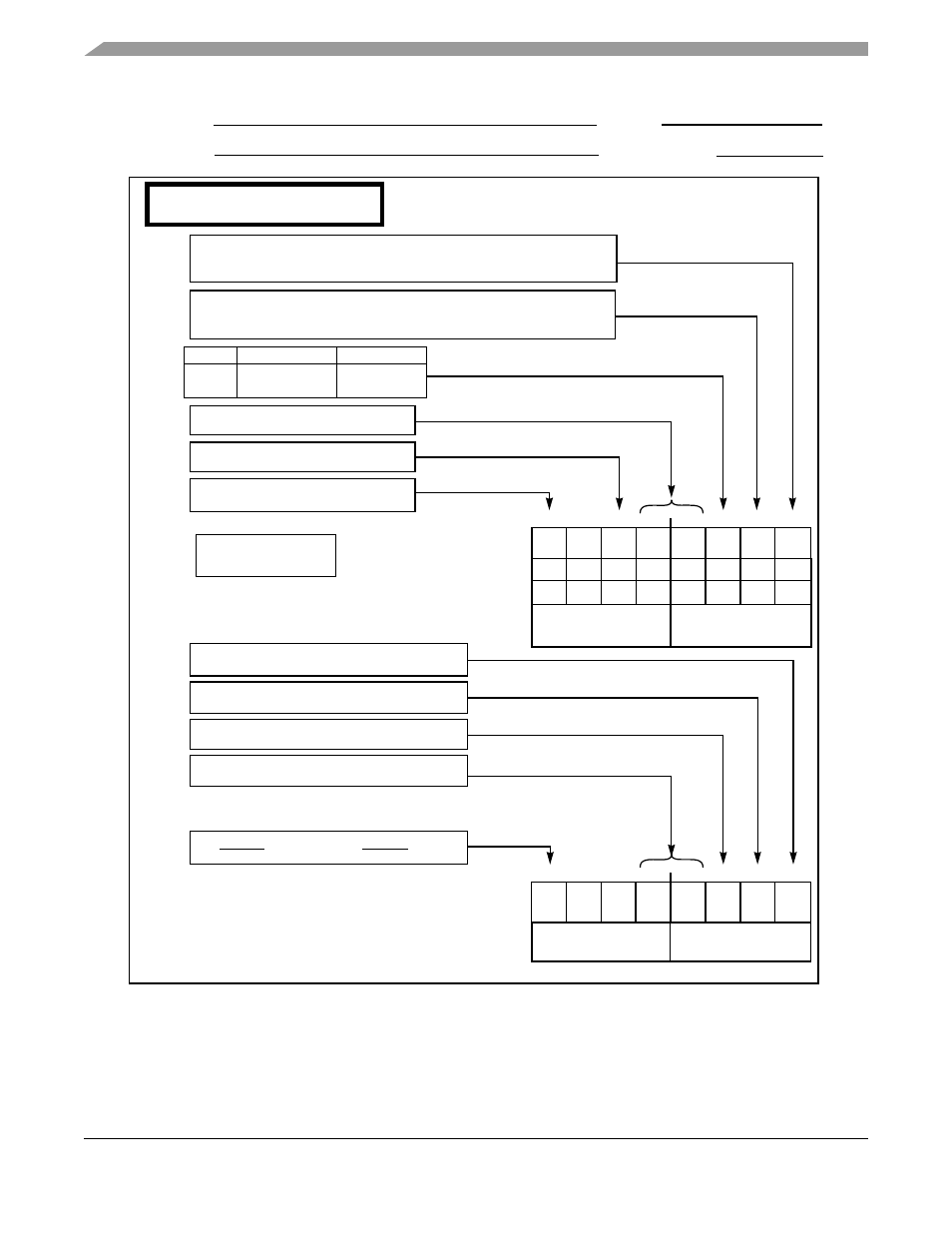

Figure D-9. Host Interrupt Control and Interrupt Status

Application:

Date:

Programmer:

Sheet 4 of 6

HOST (HDI08)

7

6

5

4

3

2

1

0

Processor Side

RREQ

HF1

TREQ

HF0

INIT

HLEND

Transmit Request Enable

DMA Off

0 = Interrupts Disabled

1 = Interrupts Enabled

DMA On

0 = DSP -> Host

1 = Host -> DSP

Host Flags

Write Only

Initialize (Write Only)

Host Little Endian

Receive Request Enable

DMA Off

0 = Interrupts Disabled

1 = Interrupts Enabled

DMA On

0 = Host -> DSP

1 = DSP -> Host

0 = No Action

1 = Initialize DMA

HDRQ

*

0

HDRQ

HOREQ/HTRQ

HACK/HRRQ

0

HOREQ

HACK

1

HTRQ

HRRQ

7

6

5

4

3

2

1

0

*

= Reserved, Program as 0

*

0

RXDF

HF3

TXDE

HF2

HREQ

TRDY

Interrupt Status Register (ISR)

$2 R/W

Reset = $0

Transmit Data Register Empty

0 = Wait

1 = Write

Transmitter Ready

0 = Data in HI

1 = Data Not in HI

Host Flags

Read Only

Receive Data Register Full

0 = Wait

1 = Read

Host Request

0 = HOREQ Deasserted 1 = HOREQ Asserted

INIT

INIT

HM1

(HDM1)

HM0

HF1

(HDM0) HF1

HF0

HF0

Interrupt Control Register (ICR)

HDM[2:0] = 100

HDM1 and/or HDM0 = 1

TREQ

TREQ

RREQ

RREQ

For HM[1:0] bits, see

Table 6-12 in Section 6

0

*

$0 R/W

Reset = $0

*

0

*

0

HDM[2:0] = 000