3 memory configuration, 1 data and program memory maps, Memory configuration -1 – Freescale Semiconductor DSP56366 User Manual

Page 57: Data and program memory maps -1, Table 3-1, Internal memory configurations -1, Peripheral configurations. refer to, Section 3, "memory configuration

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor

3-1

3

Memory Configuration

3.1

Data and Program Memory Maps

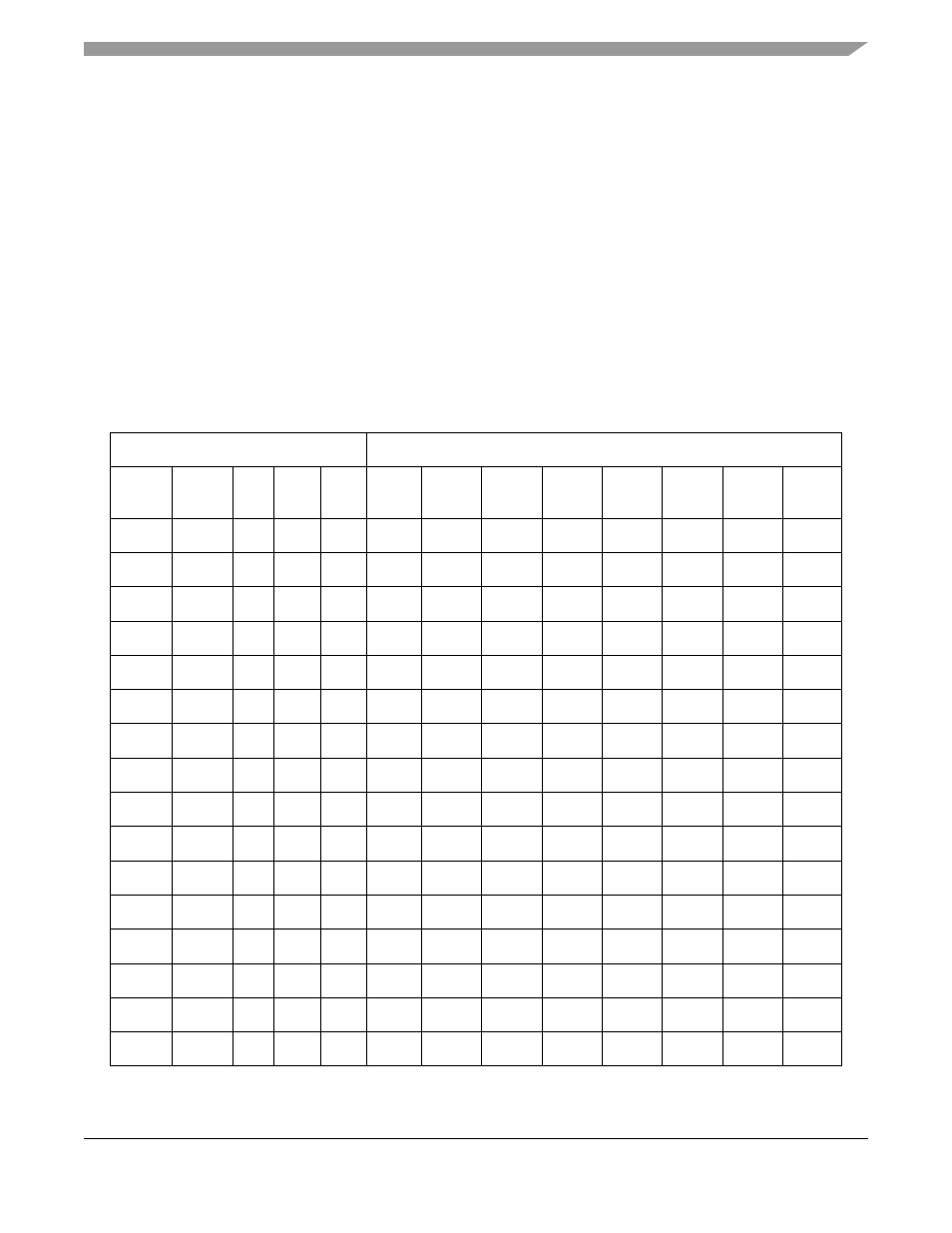

The on-chip memory configuration of the DSP56366 is affected by the state of the CE (Cache Enable),

MSW0, MSW1, and MS (Memory Switch) control bits in the OMR register, and by the SC bit in the Status

Register. The internal data and program memory configurations are shown in

ranges for the internal memory are shown in

and

. The memory maps for each memory

configuration are shown in

Table 3-1 Internal Memory Configurations

Bit Settings

Memory Sizes (24-bit words)

MSW1

MSW0

CE

MS

SC

Prog

RAM

Prog

Cache

Prog

ROM

Boot

ROM

X Data

RAM

Y Data

RAM

X Data

ROM

Y Data

ROM

X

X

0

0

0

3K

n.a.

40K

192

13K

7K

32K

8K

X

X

1

0

0

2K

1K

40K

192

13K

7K

32K

8K

0

0

0

1

0

10K

n.a.

40K

192

8K

5K

32K

8K

0

1

0

1

0

8K

n.a.

40K

192

8K

7K

32K

8K

1

0

0

1

0

5K

n.a.

40K

192

11K

7K

32K

8K

0

0

1

1

0

9K

1K

40K

192

8K

5K

32K

8K

0

1

1

1

0

7K

1K

40K

192

8K

7K

32K

8K

1

0

1

1

0

4K

1K

40K

192

11K

7K

32K

8K

X

X

0

0

1

3K

n.a.

n.a.

n.a.

13K

7K

32K

8K

X

X

1

0

1

2K

1K

n.a.

n.a.

13K

7K

32K

8K

0

0

0

1

1

10K

n.a.

n.a.

n.a.

8K

5K

32K

8K

0

1

0

1

1

8K

n.a.

n.a.

n.a.

8K

7K

32K

8K

1

0

0

1

1

5K

n.a.

n.a.

n.a.

11K

7K

32K

8K

0

0

1

1

1

9K

1K

n.a.

n.a.

8K

5K

32K

8K

0

1

1

1

1

7K

1K

n.a.

n.a.

8K

7K

32K

8K

1

0

1

1

1

4K

1K

n.a.

n.a.

11K

7K

32K

8K