3 icr double host request (hdrq) bit 2, 4 icr host flag 0 (hf0) bit 3, 5 icr host flag 1 (hf1) bit 4 – Freescale Semiconductor DSP56366 User Manual

Page 115: Icr double host request (hdrq) bit 2 -21, Icr host flag 0 (hf0) bit 3 -21, Icr host flag 1 (hf1) bit 4 -21, Table 6-9, Table 6-10, Treq rreq dma mode (hm1¼0 or hm0¼0) -21, Table 6-11

HDI08 – External Host Programmer’s Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor

6-21

6.6.1.3

ICR Double Host Request (HDRQ) Bit 2

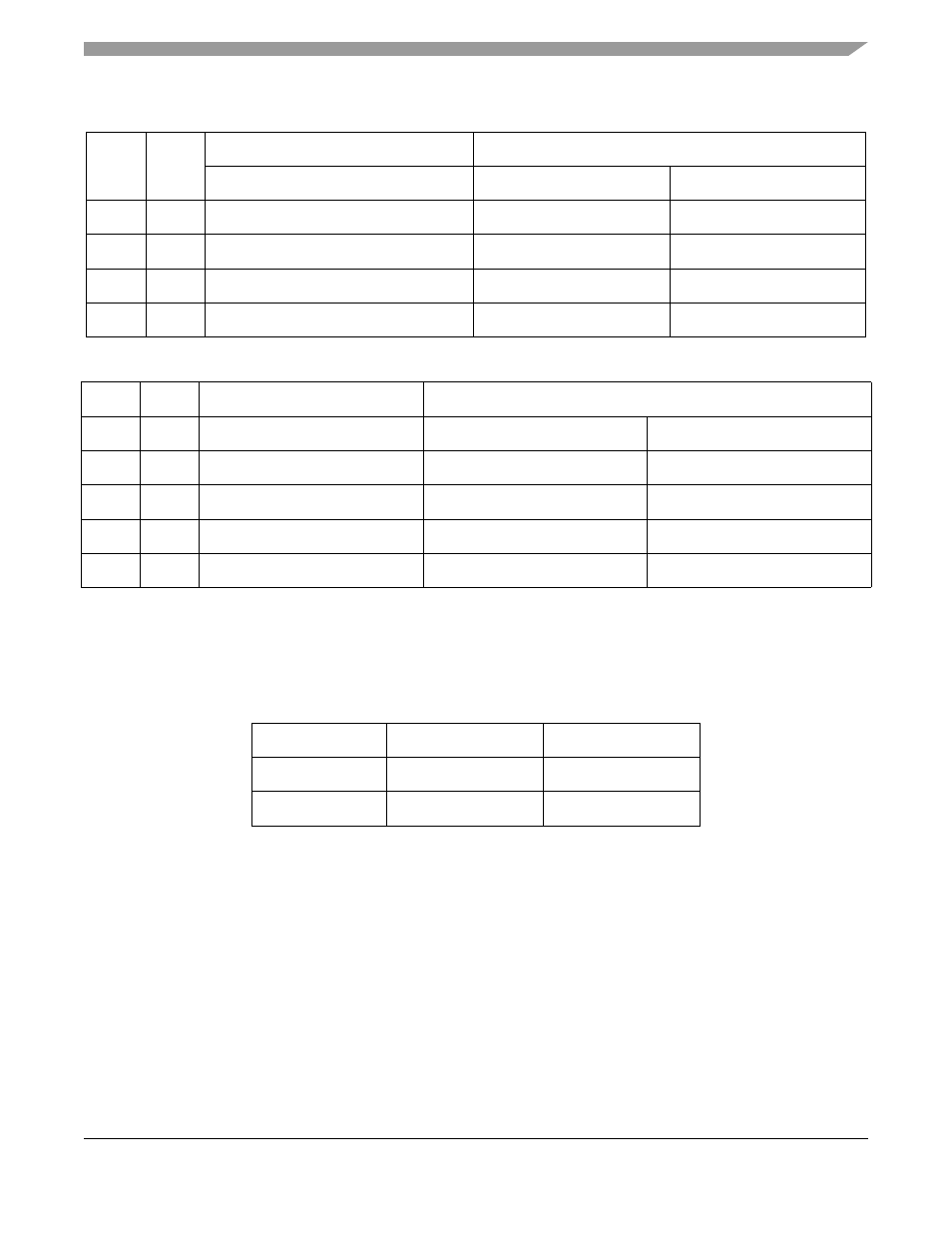

The HDRQ bit determines the functions of the HOREQ/HTRQ and HACK/HRRQ signals as shown in

6.6.1.4

ICR Host Flag 0 (HF0) Bit 3

The HF0 bit is used as a general purpose flag for host-to-DSP communication. HF0 may be set or cleared

by the host processor and cannot be changed by the DSP core. HF0 is reflected in the HSR on the DSP side

of the HDI08.

6.6.1.5

ICR Host Flag 1 (HF1) Bit 4

The HF1 bit is used as a general purpose flag for host-to-DSP communication. HF1 may be set or cleared

by the host processor and cannot be changed by the DSP core. HF1 is reflected in the HSR on the DSP side

of the HDI08.

Table 6-9 TREQ RREQ Interrupt Mode (HDM[2:0]=000 or HM[1:0]=00)

TREQ

RREQ

HDRQ=0

HDRQ=1

HOREQ signal

HTRQ signal

HRRQ signal

0

0

No Interrupts (Polling)

No Interrupts (Polling)

No Interrupts (Polling)

0

1

RXDF Request (Interrupt)

No Interrupts (Polling)

RXDF Request (Interrupt)

1

0

TXDE Request (Interrupt)

TXDE Request (Interrupt)

No Interrupts (Polling)

1

1

RXDF and TXDE Requests (Interrupts)

TXDE Request (Interrupt)

RXDF Request (Interrupt)

Table 6-10 TREQ RREQ DMA Mode (HM1

≠0 or HM0≠0)

TREQ

RREQ

HDRQ=0

HDRQ=1

HOREQ signal

HTRQ signal

HRRQ signal

0

0

No DMA request

No DMA request

No DMA request

0

1

DSP to Host Request (RX)

No DMA request

DSP to Host Request (RX)

1

0

Host to DSP Request (TX)

Host to DSP Request (TX)

No DMA request

1

1

Reserved

Reserved

Reserved

Table 6-11 HDRQ

HDRQ

HOREQ/HTRQ pin

HACK/HRRQ pin

0

HOREQ signal

HACK signal

1

HTRQ signal

HRRQ signal