5 external memory support, 2 internal i/o memory map, External memory support -12 – Freescale Semiconductor DSP56366 User Manual

Page 68: Internal i/o memory map -12, Table 3-4

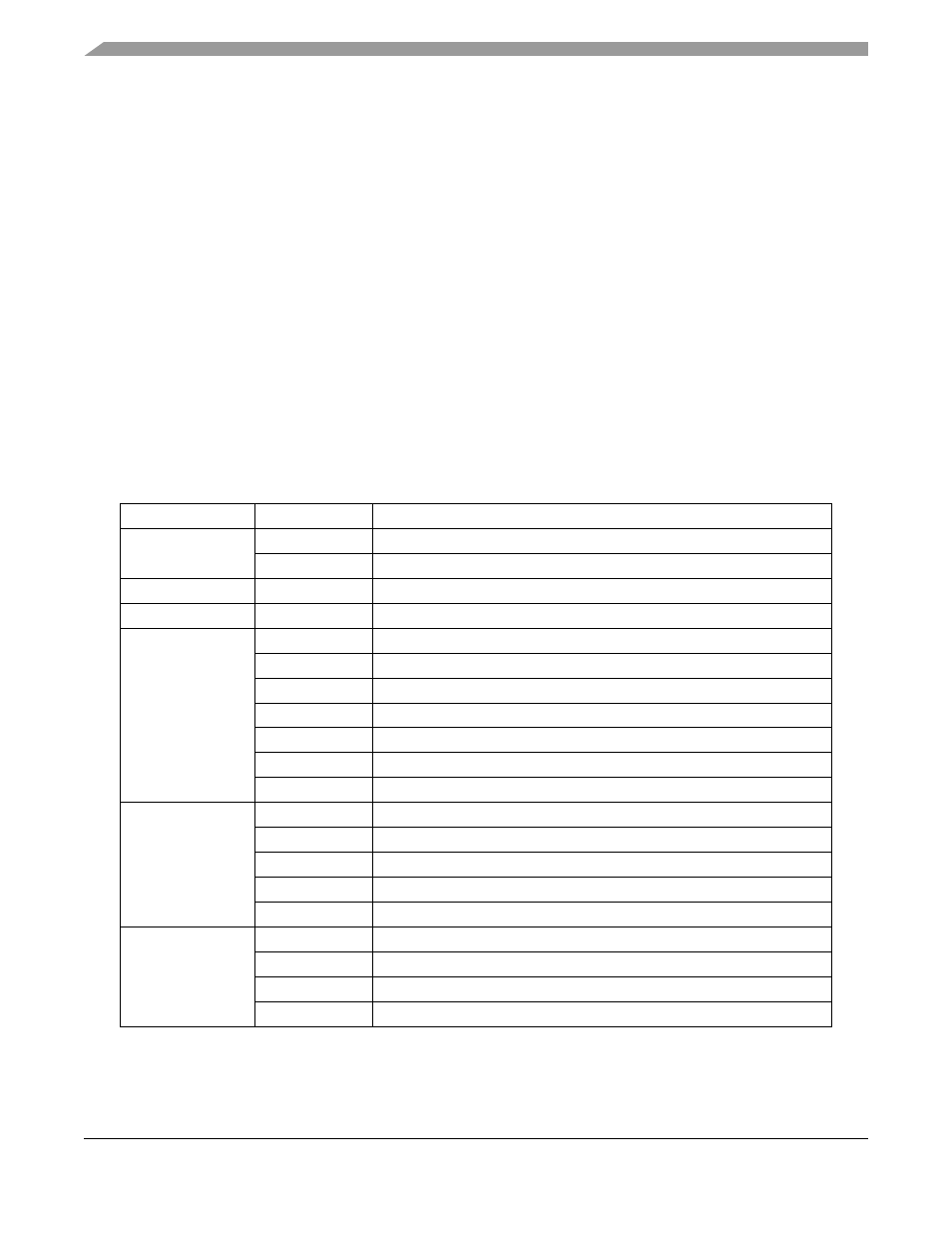

Internal I/O Memory Map

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

3-12

Freescale Semiconductor

while the DSP is in Debug mode. As a result, subsequent instructions might be fetched according to the

new memory configuration (after the switch), and thus might execute improperly.

3.1.5

External Memory Support

The DSP56366 does not support the SSRAM memory type. It does support SRAM and DRAM as

indicated in the

DSP56300 24-Bit Digital Signal Processor Family Manual

, Freescale publication

DSP56300FM. Also, care should be taken when accessing external memory to ensure that the necessary

address lines are available. For example, when using glueless SRAM interfacing, it is possible to directly

address 3

× 2

18

memory locations (768k) when using the 18 address lines and the three programmable

address attribute lines.

3.2

Internal I/O Memory Map

The DSP56366 on-chip peripheral modules have their register files programmed to the addresses in the

internal X-I/O memory range (the top 128 locations of the X data memory space) and internal Y-I/O

memory range (48 locations of the Y-data memory space) as shown in

Table 3-4 Internal I/O Memory Map

Peripheral

Address

Register Name

IPR

X:$FFFFFF

INTERRUPT PRIORITY REGISTER CORE (IPR-C)

X:$FFFFFE

INTERRUPT PRIORITY REGISTER PERIPHERAL (IPR-P)

PLL

X:$FFFFFD

PLL CONTROL REGISTER (PCTL)

ONCE

X:$FFFFFC

ONCE GDB REGISTER (OGDB)

BIU

X:$FFFFFB

BUS CONTROL REGISTER (BCR)

X:$FFFFFA

DRAM CONTROL REGISTER (DCR)

X:$FFFFF9

ADDRESS ATTRIBUTE REGISTER 0 (AAR0)

X:$FFFFF8

ADDRESS ATTRIBUTE REGISTER 1 (AAR1)

X:$FFFFF7

ADDRESS ATTRIBUTE REGISTER 2 (AAR2)

X:$FFFFF6

ADDRESS ATTRIBUTE REGISTER 3 (AAR3) [pin not available]

X:$FFFFF5

ID REGISTER (IDR)

DMA X:$FFFFF4

DMA

STATUS REGISTER (DSTR)

X:$FFFFF3

DMA OFFSET REGISTER 0 (DOR0)

X:$FFFFF2

DMA OFFSET REGISTER 1 (DOR1)

X:$FFFFF1

DMA OFFSET REGISTER 2 (DOR2)

X:$FFFFF0

DMA OFFSET REGISTER 3 (DOR3)

DMA0

X:$FFFFEF

DMA SOURCE ADDRESS REGISTER (DSR0)

X:$FFFFEE

DMA DESTINATION ADDRESS REGISTER (DDR0)

X:$FFFFED

DMA COUNTER (DCO0)

X:$FFFFEC

DMA CONTROL REGISTER (DCR0)