Esai_1 – Freescale Semiconductor DSP56366 User Manual

Page 347

Programming Sheets

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor

D-39

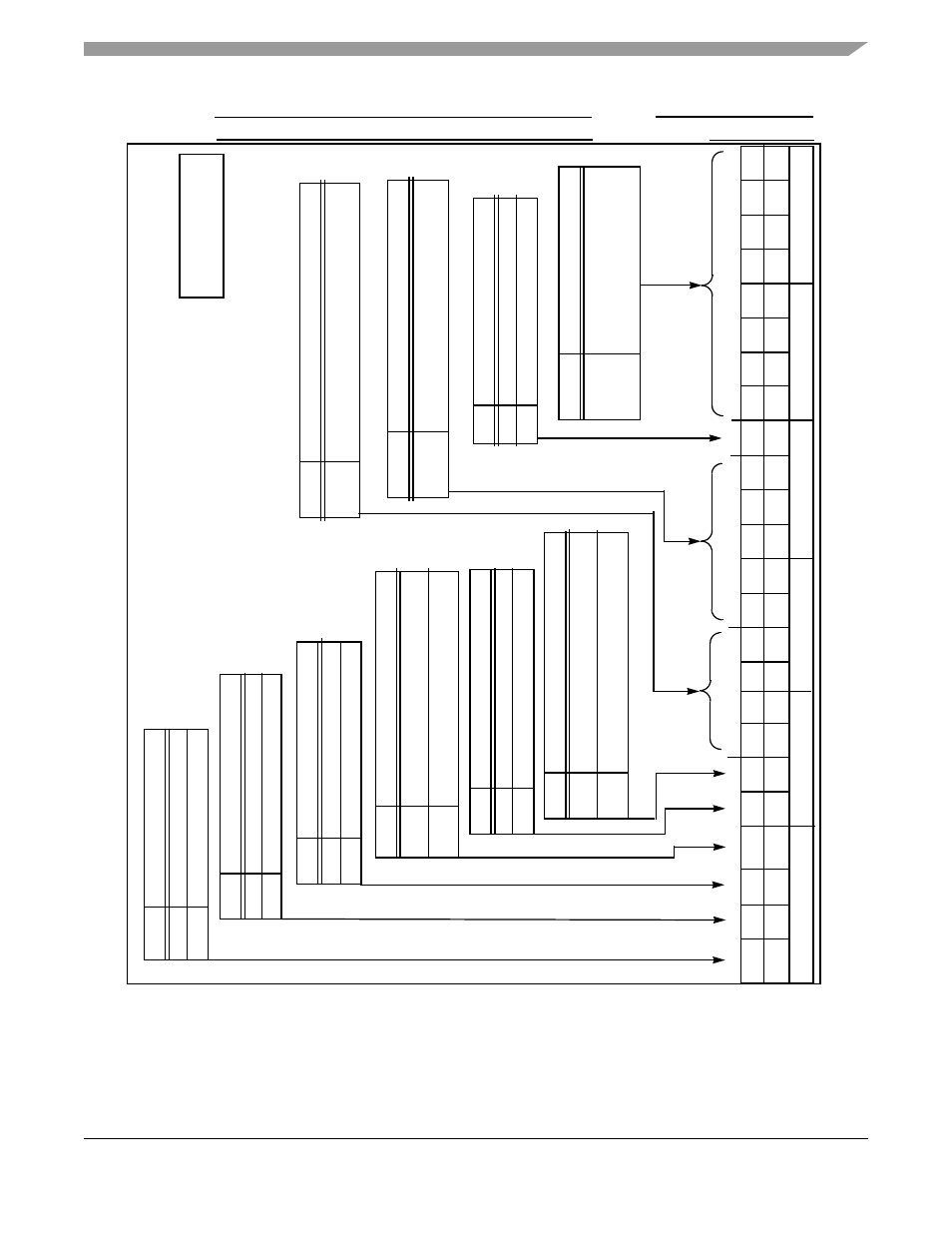

Figure D-24. ESAI_1 Receive Clock Control Register

15

6

5

4

19

18

17

16

10

9

8

7

14

13

12

11

RPM0

32

10

RPM

2

23

22

21

20

RPM1

RP

M

3

RPM

4

RPM

5

RPM6

RPM7

RPSR

RDC0

R

DC1

RDC2

RDC3

RDC4

RFP0

RFP1

RFP2

RFP3

RCKP

RF

S

P

R

HCKP

RCKD

RFSD

RHCKD

RC

KP

Desc

ription

0

1

C

lockout on

rising

edge

of

re

ceive

cl

oc

k,

latch

in on f

all

in

g

ed

ge of

r

eceive

clock

C

lockout on

falling

edge

of rece

ive

clock,

latch

in on r

ising edge of

receive clock

RFS

P

D

esc

ri

pti

o

n

0

1

Fr

am

e sync

pola

rit

y positive

Fr

am

e sync

pola

rit

y negative

RF

P [

3:

0]

D

escri

pt

io

n

Sets di

vide

rate

RCKD

Descri

p

ti

o

n

0

1

E

xt

er

nal cl

ock so

urce used

Int

er

nal clock sour

ce

RFSD

De

sc

ript

io

n

0

1

F

S

R_

1 is inp

ut

F

S

R_

1 is ou

tp

ut

RH

CK

D

Description

0

1

Re

se

rv

ed

Mu

st be set for proper operati

on

RHC

KP

De

scription

0

1

K

eep cle

ar

ed for

pr

oper

operati

on

Re

se

rv

ed

R

ange

$0 - $F (1 -

16)

.

RDC [4

:0

]

D

e

s

c

ri

p

ti

on

Co

ntrols fram

e

ra

te d

ivid

e

rs

R

P

M [7:0]

D

escription

Spe

cifies pre

sc

aler ratio for

the

RPSR

De

scription

0

1

Di

vi

de

by

8 pr

es

cal

er

oper

at

ional

Di

vi

de

by

8 pr

es

cal

er

by

pas

se

d

Rang

e

fr

om

$00 -

$FF (

1 -

256).

re

ceive cl

oc

k

ge

ner

at

or

RCCR_1 - ESAI_1 Receive Clock Control Register Y: $FFFF98 Reset: $000000

R

ange

000

00 -

11111 (

1-

32)

Application:

Date:

Programmer:

ESAI_1