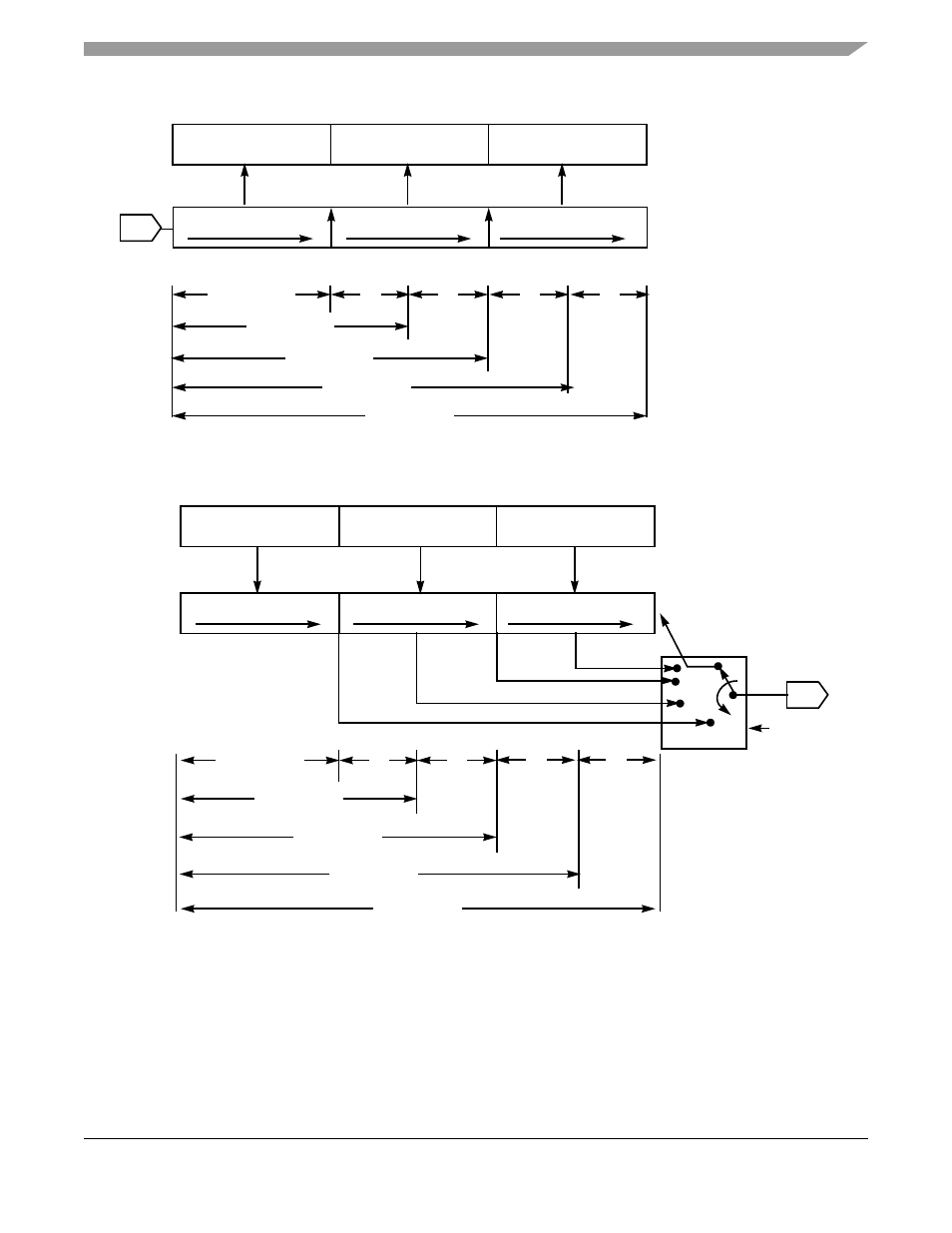

Figure 8-14, Esai data path programming model ([r/t]shfd=1) -39, A) receive registers – Freescale Semiconductor DSP56366 User Manual

Page 189: B) transmit registers

ESAI Programming Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor

8-39

Figure 8-14 ESAI Data Path Programming Model ([R/T]SHFD=1)

SDI

23

16 15870

7

0

7070

RECEIVE HIGH BYTERECEIVE MIDDLE BYTERECEIVE LOW BYTE

ESAI RECEIVE DATA REGISTER

(READ ONLY)

ESAI RECEIVE

SHIFT REGISTER

23

16 15870

7

0

7070

RECEIVE HIGH BYTERECEIVE MIDDLE BYTERECEIVE LOW BYTE

24-BIT DATA

0

0

16-BIT DATA

12-BIT DATA

8-BIT DATA

LSB

LSB

LSB

LSB

MSB

MSB

MSB

MSB

LEAST SIGNIFICANT

ZERO FILL

NOTES:

1. Data is received LSB first if RSHFD=1.

2. 24-bit fractional format (ALC=0).

3. 32-bit mode is not shown.

(a) Receive Registers

SDO

23

16 15870

7

0

7070

TRANSMIT HIGH BYTETRANSMIT MIDDLE BYTETRANSMIT LOW BYTE

ESAI TRANSMIT DATA

REGISTER

(WRITE ONLY)

ESAI TRANSMIT

SHIFT REGISTER

23

16 15870

7

0

7070

TRANSMIT HIGH BYTETRANSMIT MIDDLE BYTETRANSMIT LOW BYTE

24 BIT

TSWS4-

TSWS0

24-BIT DATA

0

0

16-BIT DATA

12-BIT DATA

8-BIT DATA

LSB

LSB

LSB

LSB

MSB

MSB

MSB

MSB

NOTES:

1. Data is sent LSB first if TSHFD=1.

2. 24-bit fractional format (ALC=0).

3. 32-bit mode is not shown.

4. Data word is left aligned (TWA=0,PADC=1).

16 BIT

12 BIT

8 BIT

(b) Transmit Registers

0

0

20-BIT DATA

LSB

MSB

20 BIT

LSB

MSB

20-BIT DATA

0

0