Freescale Semiconductor DSP56366 User Manual

Page 313

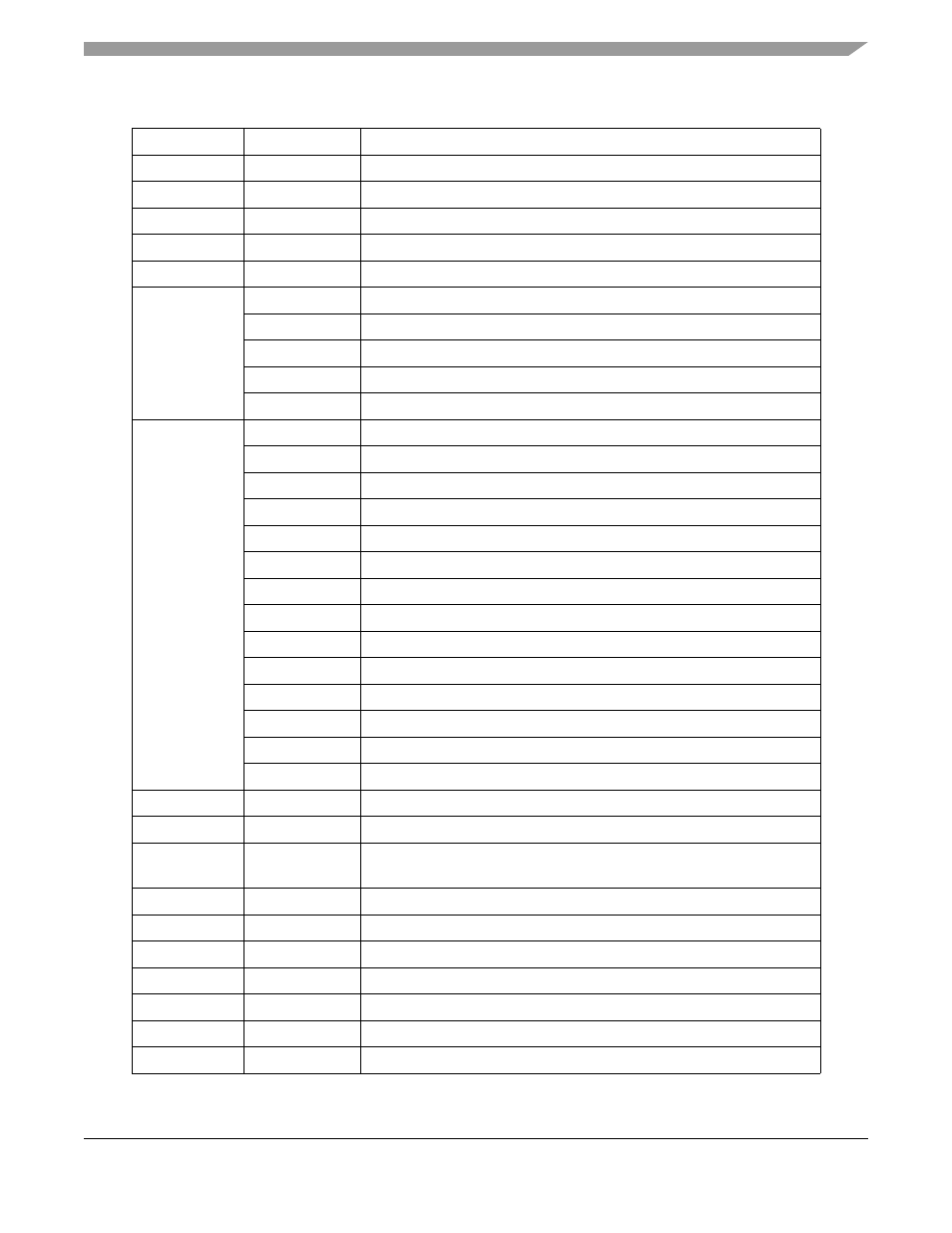

Internal I/O Memory Map

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor

D-5

X:$FFFF99

Reserved

X:$FFFF98

Reserved

X:$FFFF97

Reserved

X:$FFFF96

Reserved

X:$FFFF95

Reserved

SHI

X:$FFFF94

SHI RECEIVE FIFO (HRX)

X:$FFFF93

SHI TRANSMIT REGISTER (HTX)

X:$FFFF92

SHI I

2

C SLAVE ADDRESS REGISTER (HSAR)

X:$FFFF91

SHI CONTROL/STATUS REGISTER (HCSR)

X:$FFFF90

SHI CLOCK CONTROL REGISTER (HCKR)

TRIPLE TIMER

X:$FFFF8F

TIMER 0 CONTROL/STATUS REGISTER (TCSR0)

X:$FFFF8E

TIMER 0 LOAD REGISTER (TLR0)

X:$FFFF8D

TIMER 0 COMPARE REGISTER (TCPR0)

X:$FFFF8C

TIMER 0 COUNT REGISTER (TCR0)

X:$FFFF8B

TIMER 1 CONTROL/STATUS REGISTER (TCSR1)

X:$FFFF8A

TIMER 1 LOAD REGISTER (TLR1)

X:$FFFF89

TIMER 1 COMPARE REGISTER (TCPR1)

X:$FFFF88

TIMER 1 COUNT REGISTER (TCR1)

X:$FFFF87

TIMER 2 CONTROL/STATUS REGISTER (TCSR2)

X:$FFFF86

TIMER 2 LOAD REGISTER (TLR2)

X:$FFFF85

TIMER 2 COMPARE REGISTER (TCPR2)

X:$FFFF84

TIMER 2 COUNT REGISTER (TCR2)

X:$FFFF83

TIMER PRESCALER LOAD REGISTER (TPLR)

X:$FFFF82

TIMER PRESCALER COUNT REGISTER (TPCR)

X:$FFFF81

Reserved

X:$FFFF80

Reserved

ESAI MUX PIN

CONTROL

Y:$FFFFAF

ESAI MUX PIN CONTROL REGISTER (EMUXR)

Y:$FFFFAE

Reserved

Y:$FFFFAD

Reserved

Y:$FFFFAC

Reserved

Y:$FFFFAB

Reserved

Y:$FFFFAA

Reserved

Y:$FFFFA9

Reserved

Y:$FFFFA8

Reserved

Table D-1. Internal I/O Memory Map (continued)

Peripheral

Address

Register Name