Table d-1 – Freescale Semiconductor DSP56366 User Manual

Page 310

Internal I/O Memory Map

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

D-2

Freescale Semiconductor

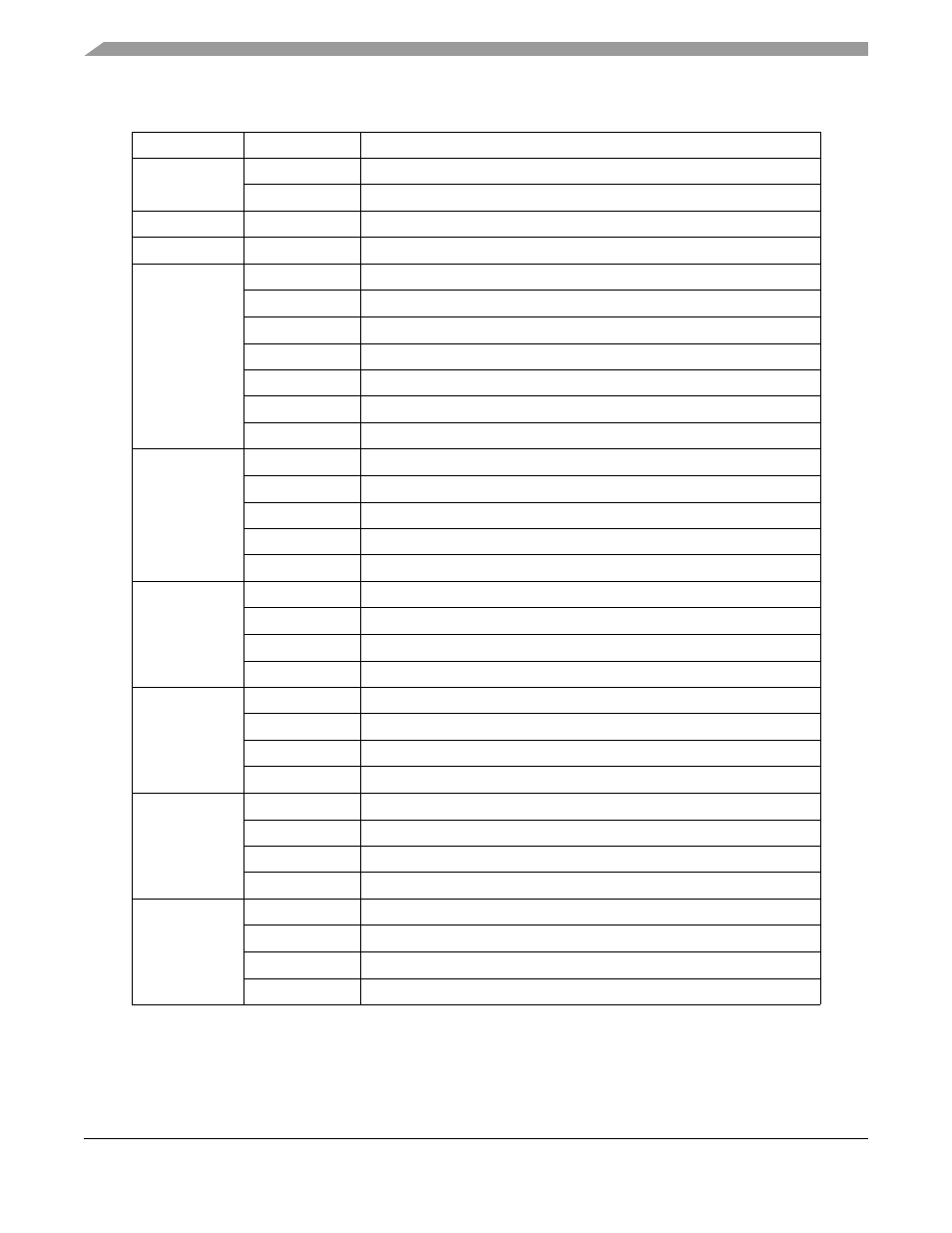

Table D-1. Internal I/O Memory Map

Peripheral

Address

Register Name

IPR

X:$FFFFFF

INTERRUPT PRIORITY REGISTER CORE (IPR-C)

X:$FFFFFE

INTERRUPT PRIORITY REGISTER PERIPHERAL (IPR-P)

PLL

X:$FFFFFD

PLL CONTROL REGISTER (PCTL)

ONCE

X:$FFFFFC

ONCE GDB REGISTER (OGDB)

BIU

X:$FFFFFB

BUS CONTROL REGISTER (BCR)

X:$FFFFFA

DRAM CONTROL REGISTER (DCR)

X:$FFFFF9

ADDRESS ATTRIBUTE REGISTER 0 (AAR0)

X:$FFFFF8

ADDRESS ATTRIBUTE REGISTER 1 (AAR1)

X:$FFFFF7

ADDRESS ATTRIBUTE REGISTER 2 (AAR2)

X:$FFFFF6

ADDRESS ATTRIBUTE REGISTER 3 (AAR3) [pin not available]

X:$FFFFF5

ID REGISTER (IDR)

DMA

X:$FFFFF4

DMA STATUS REGISTER (DSTR)

X:$FFFFF3

DMA OFFSET REGISTER 0 (DOR0)

X:$FFFFF2

DMA OFFSET REGISTER 1 (DOR1)

X:$FFFFF1

DMA OFFSET REGISTER 2 (DOR2)

X:$FFFFF0

DMA OFFSET REGISTER 3 (DOR3)

DMA0

X:$FFFFEF

DMA SOURCE ADDRESS REGISTER (DSR0)

X:$FFFFEE

DMA DESTINATION ADDRESS REGISTER (DDR0)

X:$FFFFED

DMA COUNTER (DCO0)

X:$FFFFEC

DMA CONTROL REGISTER (DCR0)

DMA1

X:$FFFFEB

DMA SOURCE ADDRESS REGISTER (DSR1)

X:$FFFFEA

DMA DESTINATION ADDRESS REGISTER (DDR1)

X:$FFFFE9

DMA COUNTER (DCO1)

X:$FFFFE8

DMA CONTROL REGISTER (DCR1)

DMA2

X:$FFFFE7

DMA SOURCE ADDRESS REGISTER (DSR2)

X:$FFFFE6

DMA DESTINATION ADDRESS REGISTER (DDR2)

X:$FFFFE5

DMA COUNTER (DCO2)

X:$FFFFE4

DMA CONTROL REGISTER (DCR2)

DMA3

X:$FFFFE3

DMA SOURCE ADDRESS REGISTER (DSR3)

X:$FFFFE2

DMA DESTINATION ADDRESS REGISTER (DDR3)

X:$FFFFE1

DMA COUNTER (DCO3)

X:$FFFFE0

DMA CONTROL REGISTER (DCR3)