1 dsp56366 overview, 1 introduction, Dsp56366 overview -1 – Freescale Semiconductor DSP56366 User Manual

Page 25: Introduction -1, Figure 1-1, Dsp56366 block diagram -1

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor

1-1

1

DSP56366 Overview

1.1

Introduction

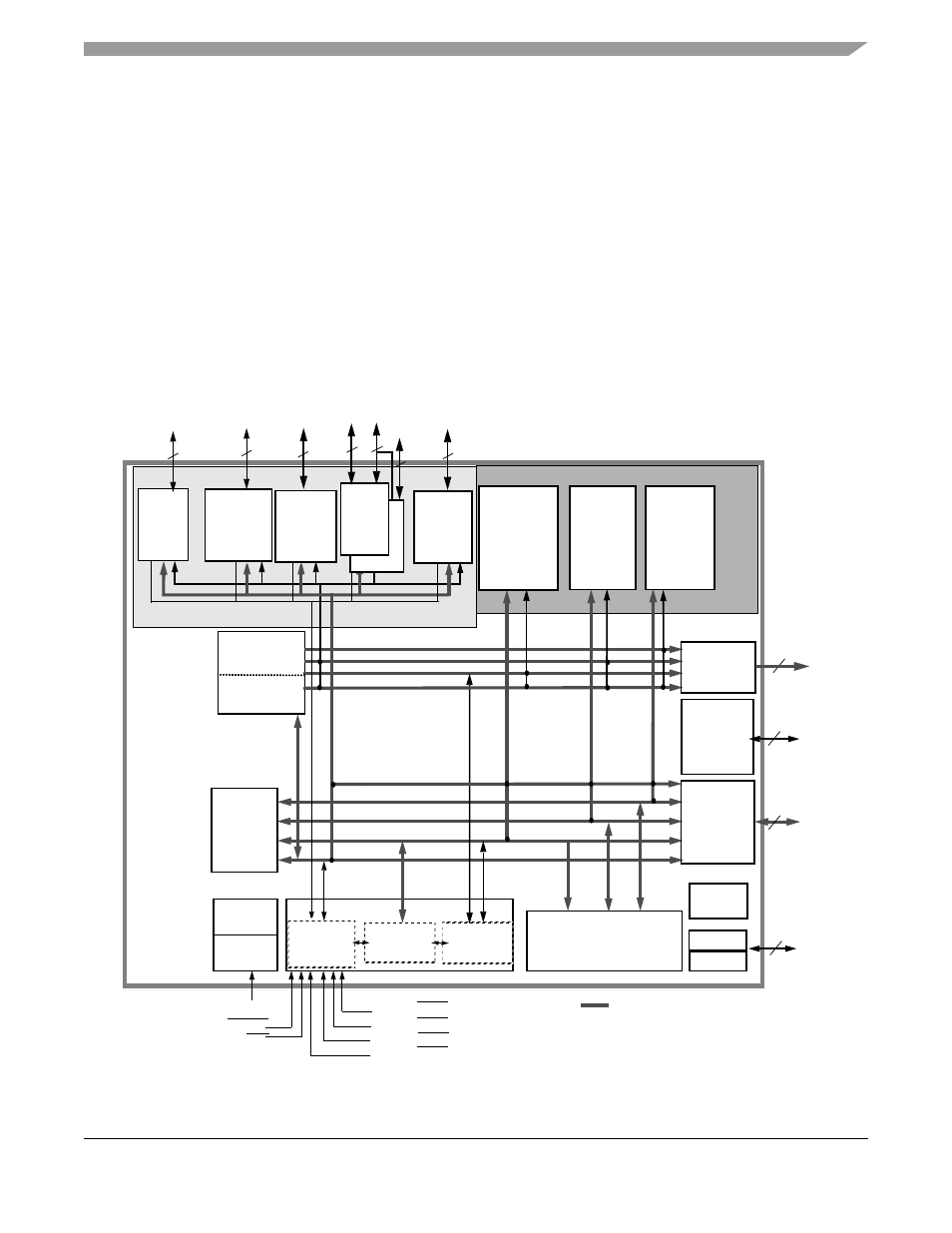

This manual describes the DSP56366 24-bit digital signal processor (DSP), its memory, operating modes,

and peripheral modules. The DSP56366 is a member of the DSP56300 family of programmable CMOS

DSPs. The DSP56366 is targeted to applications that require digital audio compression/decompression,

sound field processing, acoustic equalization and other digital audio algorithms. Changes in core

functionality specific to the DSP56366 are also described in this manual. See

diagram of the DSP56366.

Figure 1-1 DSP56366 Block Diagram

CLOCK

GENERATO

INTERNAL

DATA

BUS

EXTAL

PROGRAM

RAM

/INSTR.

CACHE

3K x 24

PROGRAM

ROM

40K x 24

Bootstrap

PROGRAM

INTERRUPT

CONTROLLER

PROGRAM

DECODE

CONTROLLE

PROGRAM

ADDRESS

GENERATOR

YAB

XAB

PAB

YDB

XDB

PDB

GDB

MODA/IRQA

MODB/IRQB

DATA ALU

24X24+56->56-BIT MAC

TWO 56-BIT ACCUMULATORS

BARREL SHIFTER

MODC/IRQC

PLL

OnCE™

HOST

INTER-

FACE

DAX

(SPDIF Tx.)

INTER-FAC

E

4

16

X MEMORY

RAM

13K X 24

ROM

32K x 24

Y MEMORY

RAM

7K X 24

ROM

8K x 24

DDB

DAB

SIX CHANNELS

DMA UNIT

MEMORY EXPANSION AREA

PERIPHERAL

YM_EB

XM_EB

PM_EB

PIO_EB

24 BITS BUS

EXPANSION AREA

JTAG

4

5

RESET

POWER

MNGMNT

PINIT/NMI

2

TRIPLE

TIMER

1

MODD/IRQD

DRAM &

SRAM BUS

INTERFACE

&

I - CACHE

EXTERNAL

ADDRESS

BUS

SWITCH

EXTERNAL

DATA BUS

SWITCH

ADDRESS

10

DATA

CONTROL

24

18

ESAI

INTER-

FACE

8

6

ESAI_1

ADDRESS

GENERATION

UNIT

24-BIT

DSP56300

Core

SHI

INTER-

FACE