3 esai_1 transmit control register (tcr_1), Esai_1 transmit control register (tcr_1) -8, Figure 9-5 – Freescale Semiconductor DSP56366 User Manual

Page 208: Figure 9-6, Tcr_1 register -8

ESAI_1 Programming Model

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

9-8

Freescale Semiconductor

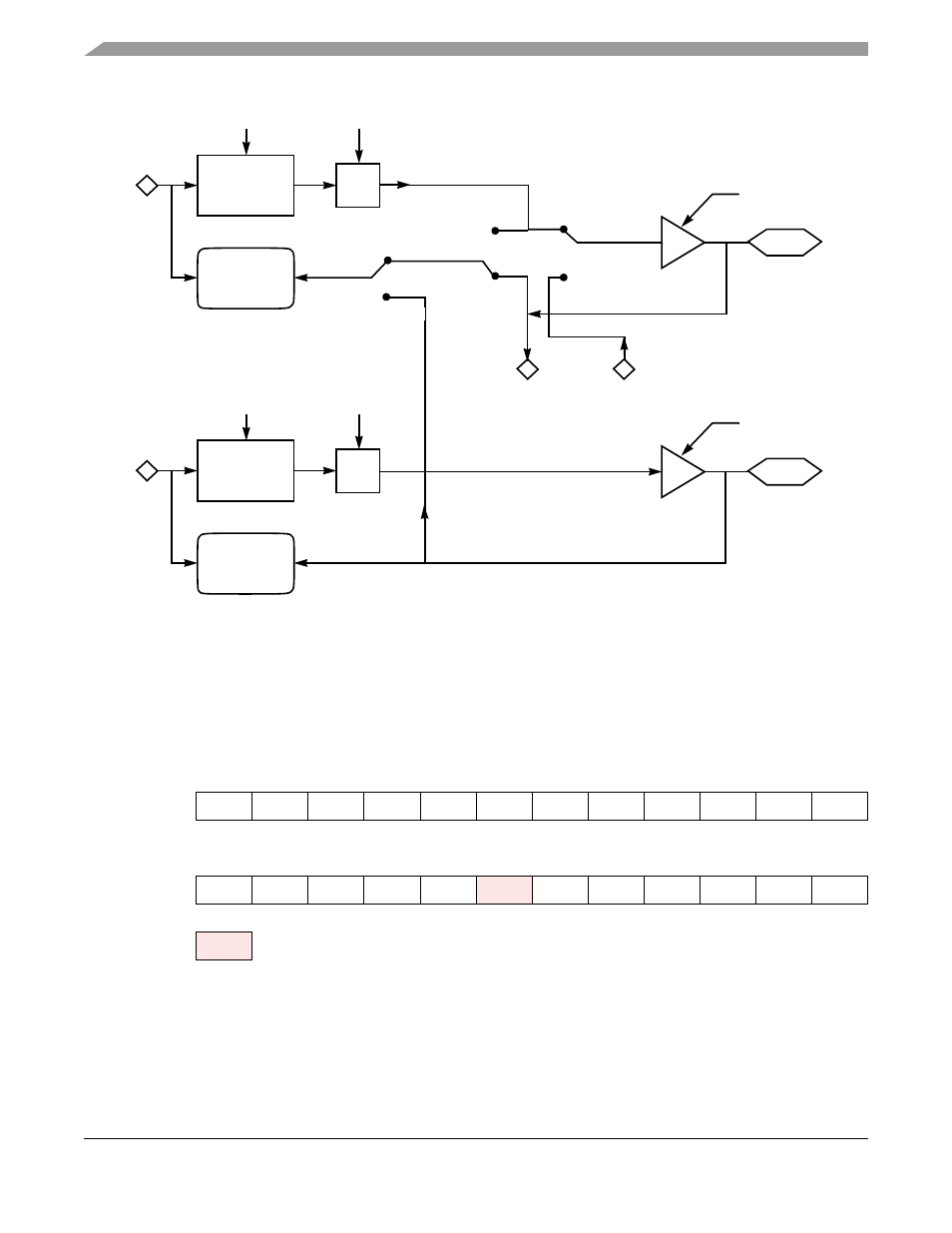

Figure 9-5 ESAI_1 Frame Sync Generator Functional Block Diagram

9.3.3

ESAI_1 Transmit Control Register (TCR_1)

The read/write Transmit Control Register (TCR_1) controls the ESAI_1 transmitter section. Interrupt

enable bits for the transmitter section are provided in this control register. Operating modes are also

selected in this register.

Hardware and software reset clear all the bits in the TCR_1 register.

11

10

9

8

7

6

5

4

3

2

1

0

Y:$FFFF95

TSWS1 TSWS0 TMOD1 TMOD0

TWA

TSHFD

TE5

TE4

TE3

TE2

TE1

TE0

23

22

21

20

19

18

17

16

15

14

13

12

TLIE

TIE

TEDIE

TEIE

TPR

PADC

TFSR

TFSL

TSWS4 TSWS3 TSWS2

Reserved bit - read as zero; should be written with zero for future compatibility.

Figure 9-6 TCR_1 Register

FRAME SYNC

TRANSMIT

FRAME SYNC

RECEIVE

RX WORD

CLOCK

TX WORD

CLOCK

RDC0 - RDC4

TDC0 - TDC4

RECEIVER

FRAME RATE

DIVIDER

TRANSMITTER

FRAME RATE

DIVIDER

RECEIVE

CONTROL

LOGIC

TRANSMIT

CONTROL

LOGIC

RFSL

TFSL

SYNC

TYPE

SYNC

TYPE

SYN=0

SYN=1

INTERNAL RX FRAME CLOCK

RFSD=1

SYN=1

RFSD=0

SYN=0

RFSD

FSR_1

TFSD

FST_1

INTERNAL TX FRAME CLOCK

FLAG1 IN

(SYNC MODE)

FLAG1OUT

(SYNC MODE)