3 port d data register (pdrd), Port d data register (pdrd) -14, Figure 10-8 – Freescale Semiconductor DSP56366 User Manual

Page 230

GPIO (PORT D) - Pins and Registers

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

10-14

Freescale Semiconductor

10.7.3

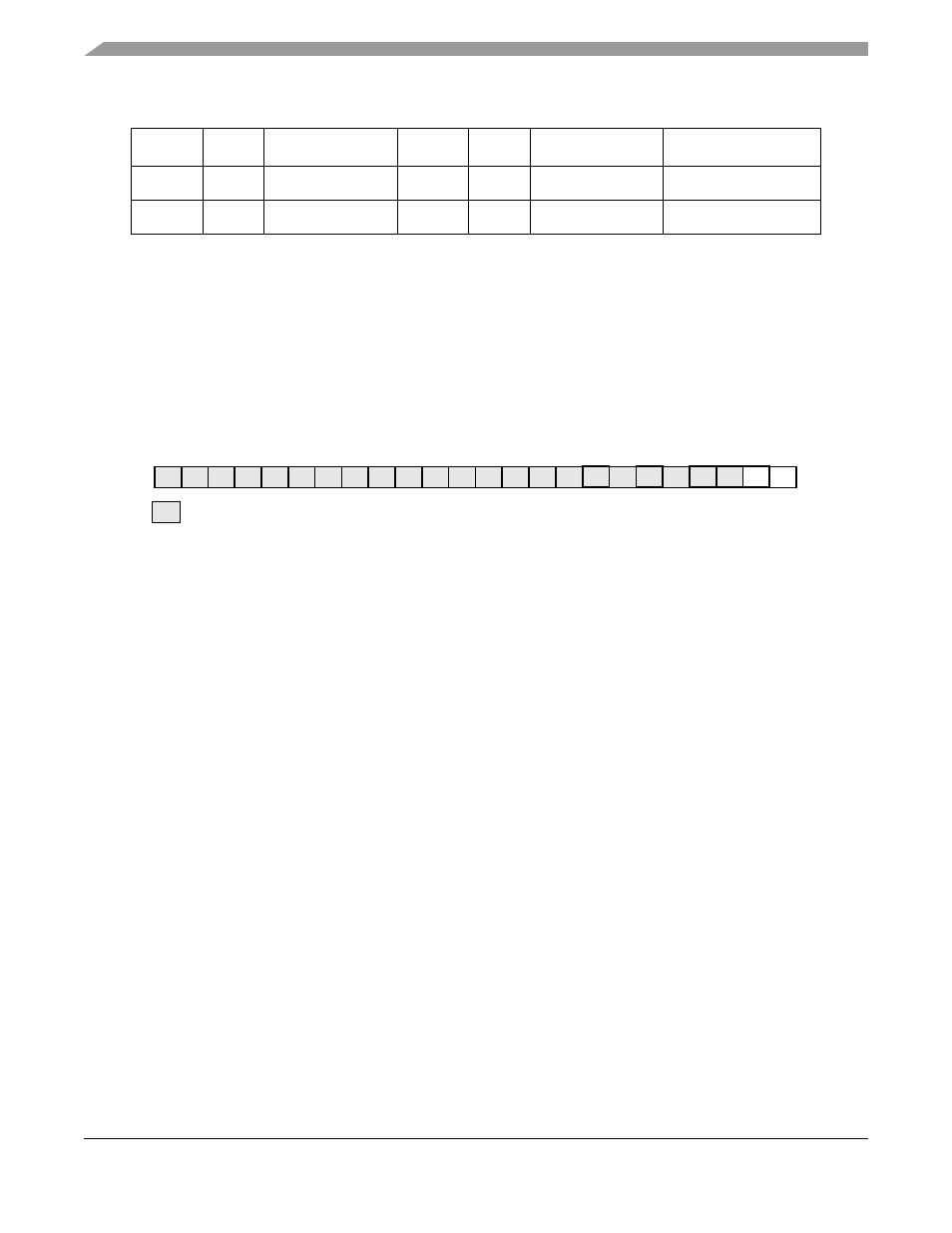

Port D Data Register (PDRD)

The read/write 24-bit Port D Data Register is used to read or write data to/from the DAX GPIO pins. Bits

PD[1:0] are used to read or write data from/to the corresponding port pins if they are configured as GPIO.

If a port pin [i] is configured as a GPIO input, then the corresponding PD[i] bit will reflect the value present

on this pin. If a port pin [i] is configured as a GPIO output, then the value written into the corresponding

PD[i] bit will be reflected on the this pin. Hardware and software reset clear all PDRD bits.

Figure 10-8 Port D Data Register (PDRD)

1

1

ADO

1

0

PD0 Output

Enabled

1

1

ADO

1

1

ACI

Enabled

Table 10-6 DAX Port GPIO Control Register Functionality

PDC1

PC1

ADO/PD1 pin

PDC0

PC0

ACI/PD0 pin

DAX state

7

PD1

1

PD0

0

4

3

2

5

6

15

12

11

10

13

14

8

9

read as zero, should be written with zero for future compatibility

23

20

19

18

21

22

16

17

PDRD - Port D Data Register - X:$FFFFD5