Figure d-5 – Freescale Semiconductor DSP56366 User Manual

Page 328

Programming Sheets

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

D-20

Freescale Semiconductor

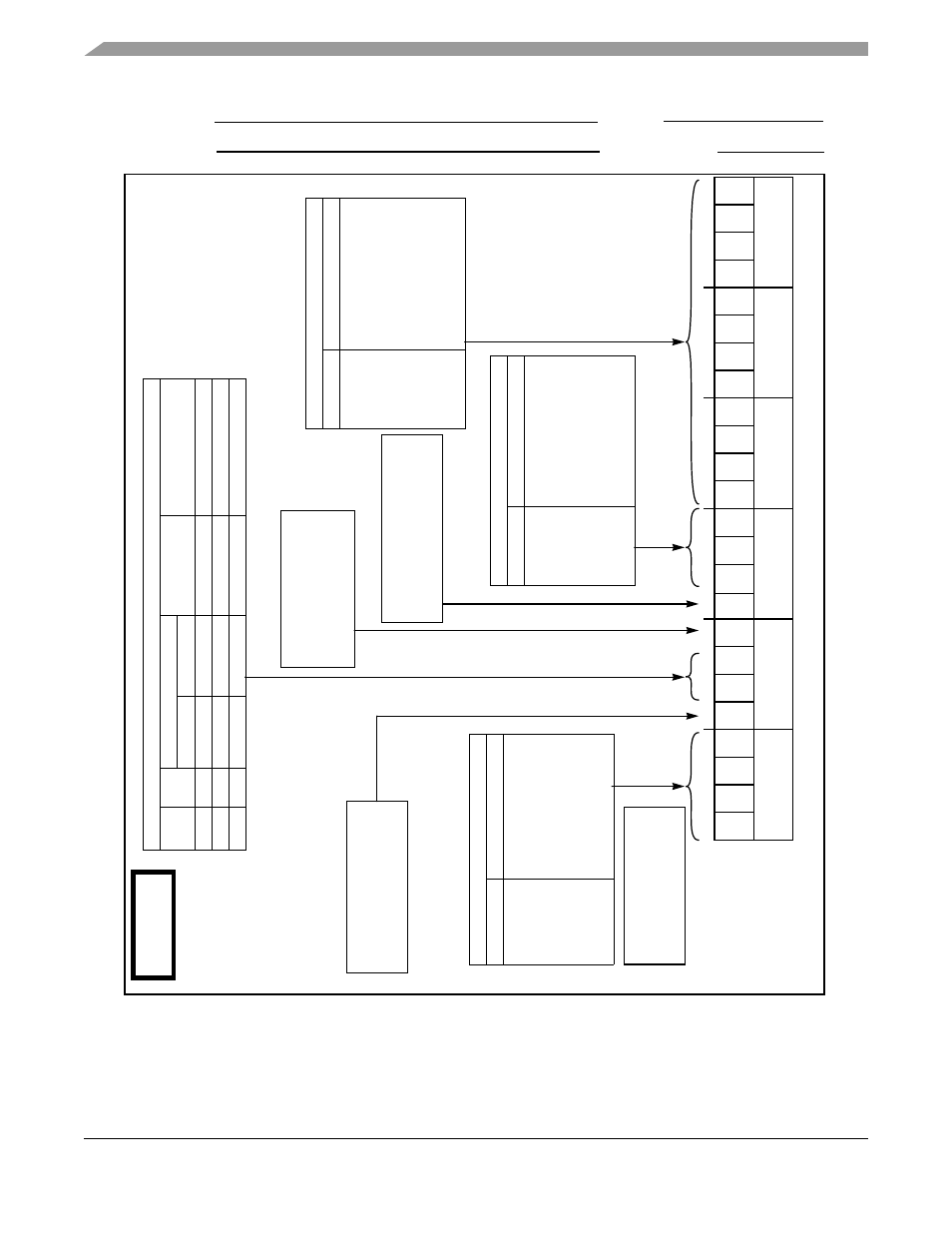

Figure D-5. Phase Lock Loop Control Register (PCTL)

Application:

Date:

Programmer:

Sheet 5 of 5

PLL

1

5

1

4

1

3

1

2

1

1

1

0

987

6543210

MF7

M

F5

M

F

4

M

F3

MF2

M

F1

MF0

19

18

17

1

6

23

22

21

20

PEN

COD

PD1

PD3

MF6

P

D

2

X

TLD

X

TLR

D

F2

DF1

D

F0

M

F

11

PD0

P

STP

M

F1

0

M

F9

MF8

PL

L Co

nt

ro

l

Reg

ister (P

C

T

L

)

X:

$FF

FFF

D Rea

d

/Write

Reset =

$0

10005

X

T

AL

Disable

Bit (

X

TLD

)

0 =

E

n

able Xtal Oscillator

1 =

E

X

T

A

L Driven From

An External Source

Clock O

u

tput

Disable

(COD)

0 = 50%

Dut

y Cycl

e Cl

ock

1

=

Pi

n Hel

d

I

n

High St

at

e

Cryst

al Ran

g

e Bit

(XT

L

R)

0

=

Extern

al Xtal Freq >200KHz

1 = External X

tal F

req <200KH

z

Prediv

ision

Fact

or Bit

s

(PD0 –

P

D

3)

PD3 – PD0

P

redivis

ion

Factor PDF

$0

$1

$2

•

•

•

$F

1

2

3

•

•

•

16

Mu

ltipli

catio

n Fa

ctor B

its MF

0 – MF11

MF11 – MF

0

M

u

ltip

licatio

n F

acto

r MF

$000

$001

$002

•

•

•

$F

FE

$F

FF

1

2

3

•

•

•

4

095

4

096

D

ivision

Factor Bits (D

F0 – DF

2)

DF

2 – DF

0

D

ivisio

n Fa

ctor D

F

$0

$1

$2

•

•

•

$7

2

0

2

1

2

2

•

•

•

2

7

PSTP and

P

E

N

Relationship

PSTP

PEN

Operation

Durin

g

STOP

Re

covery Time

fo

r STOP

P

o

wer C

onsump

tion

du

ring STOP

PLL

O

scillat

o

r

0

x

D

isabled

D

isabled

Long

Minimal

1

0

D

isabled

Enabled

Short

Lowe

r

1

1

Enabled

Enabled

Short

H

igher

No

te th

at b

its XT

LR, C

O

D

and

XTLD

have n

o

effect

on

DSP56366 o

p

eration