Freescale Semiconductor DSP56366 User Manual

Page 311

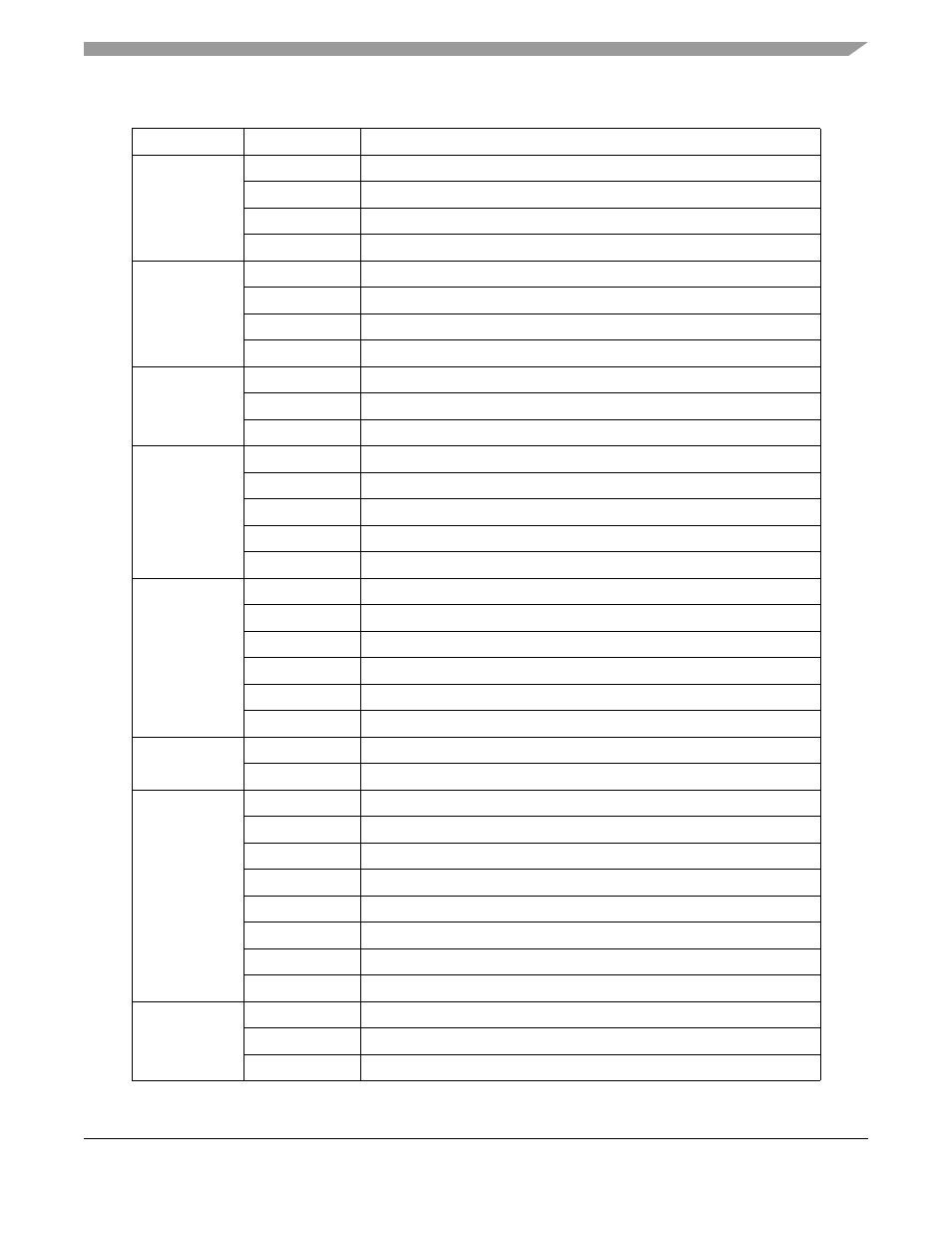

Internal I/O Memory Map

DSP56366 24-Bit Digital Signal Processor User Manual, Rev. 4

Freescale Semiconductor

D-3

DMA4

X:$FFFFDF

DMA SOURCE ADDRESS REGISTER (DSR4)

X:$FFFFDE

DMA DESTINATION ADDRESS REGISTER (DDR4)

X:$FFFFDD

DMA COUNTER (DCO4)

X:$FFFFDC

DMA CONTROL REGISTER (DCR4)

DMA5

X:$FFFFDB

DMA SOURCE ADDRESS REGISTER (DSR5)

X:$FFFFDA

DMA DESTINATION ADDRESS REGISTER (DDR5)

X:$FFFFD9

DMA COUNTER (DCO5)

X:$FFFFD8

DMA CONTROL REGISTER (DCR5)

PORT D

X:$FFFFD7

PORT D CONTROL REGISTER (PCRD)

X:$FFFFD6

PORT D DIRECTION REGISTER (PRRD)

X:$FFFFD5

PORT D DATA REGISTER (PDRD)

DAX

X:$FFFFD4

DAX STATUS REGISTER (XSTR)

X:$FFFFD3

DAX AUDIO DATA REGISTER B (XADRB)

X:$FFFFD2

DAX AUDIO DATA REGISTER A (XADRA)

X:$FFFFD1

DAX NON-AUDIO DATA REGISTER (XNADR)

X:$FFFFD0

DAX CONTROL REGISTER (XCTR)

X:$FFFFCF

Reserved

X:$FFFFCE

Reserved

X:$FFFFCD

Reserved

X:$FFFFCC

Reserved

X:$FFFFCB

Reserved

X:$FFFFCA

Reserved

PORT B

X:$FFFFC9

HOST PORT GPIO DATA REGISTER (HDR)

X:$FFFFC8

HOST PORT GPIO DIRECTION REGISTER (HDDR)

HDI08

X:$FFFFC7

HOST TRANSMIT REGISTER (HOTX)

X:$FFFFC6

HOST RECEIVE REGISTER (HORX)

X:$FFFFC5

HOST BASE ADDRESS REGISTER (HBAR)

X:$FFFFC4

HOST PORT CONTROL REGISTER (HPCR)

X:$FFFFC3

HOST STATUS REGISTER (HSR)

X:$FFFFC2

HOST CONTROL REGISTER (HCR)

X:$FFFFC1

Reserved

X:$FFFFC0

Reserved

PORT C

X:$FFFFBF

PORT C CONTROL REGISTER (PCRC)

X:$FFFFBE

PORT C DIRECTION REGISTER (PRRC)

X:$FFFFBD

PORT C GPIO DATA REGISTER (PDRC)

Table D-1. Internal I/O Memory Map (continued)

Peripheral

Address

Register Name