Register maps, Register maps –8, Table 4–9 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 96

4–8

Chapter 4: SDI Audio IP Cores

SDI Audio Embed MegaCore Function

Serial Digital Interface (SDI) MegaCore Function

February 2013

Altera Corporation

User Guide

Register Maps

lists the register maps for SDI Audio Embed MegaCore

function.

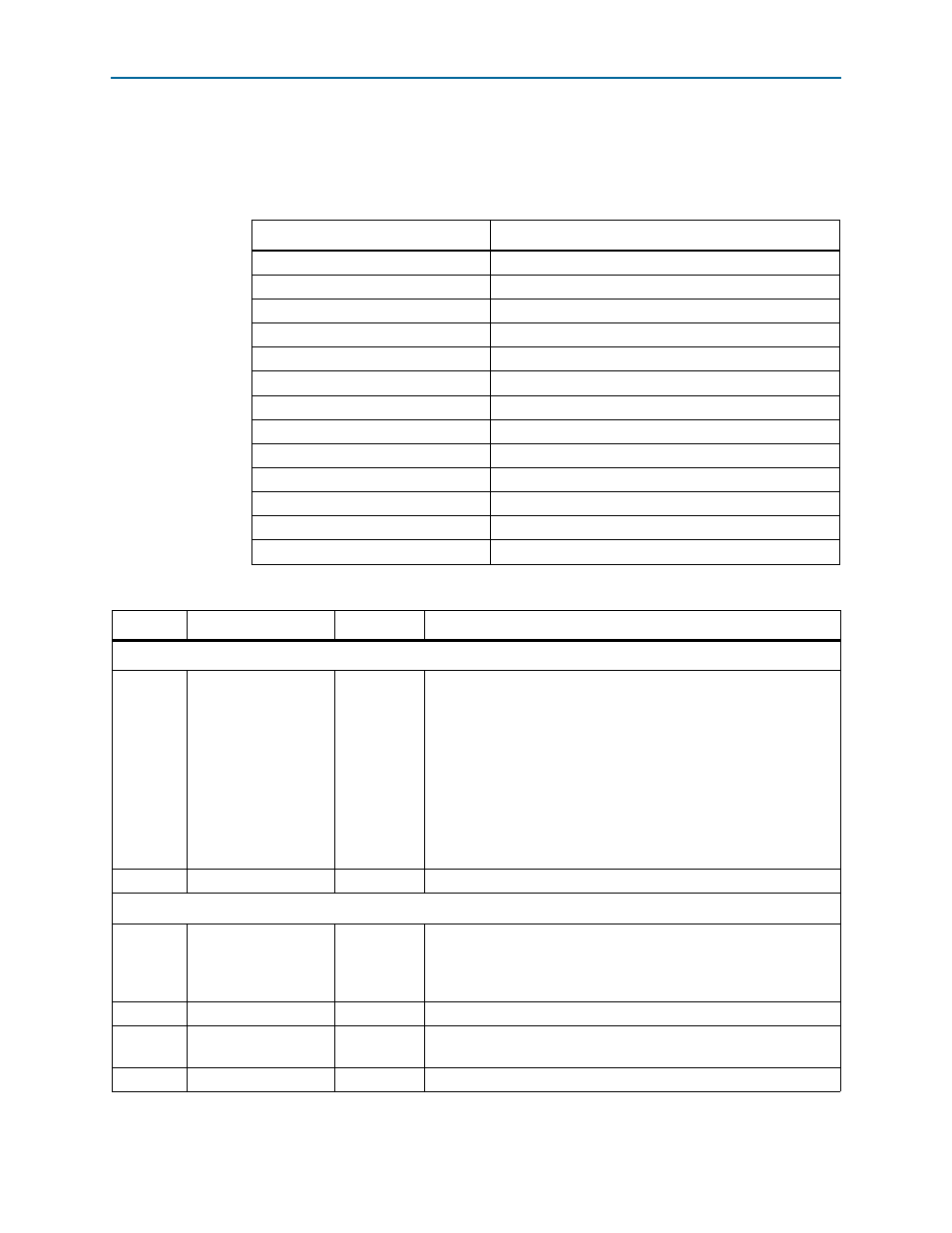

Table 4–8. SDI Audio Embed MegaCore Function Register Map

Bytes Offset

Name

00h

Audio Control Register

01h

Extended Control Register

02h

Video Status Register

03h

Audio Status Register

04h

Channel Status Control Registers (3:0)

05h

Channel Status Control Registers (7:4)

06h–07h

Reserved

08h

Sine Channel 1 Frequency

09h

Sine Channel 2 Frequency

0Ah

Sine Channel 3 Frequency

0Bh

Sine Channel 4 Frequency

0Ch–0Fh

Reserved

10h–3Fh

Channel Status RAM (0×00), (0×01), ... (0×2F)

Table 4–9. SDI Audio Embed MegaCore Function Register Map

Bit

Name

Access

Description

Audio Control Register

3:0

Audio group enable

RW

Enables the embedding of each audio group. When working with

HD-SDI or 3G-SDI video, embedding of the audio control packet is

also enabled when one or more audio groups are enabled.

The following bits correspond to the number of audio groups you

specify:

■

Bit [0] = Audio group 1

■

Bit [1] = Audio group 2

■

Bit [2] = Audio group 3

■

Bit [3] = Audio group 4

7:4

Unused

—

Reserved for future use.

Extended Control Register

2:0

Channel status RAM

select

RW

When you specify the Channel Status RAM parameter to 2, this field

selects the channel pair for the RAM written to by registers 10h to

3Fh. If you specify the Channel Status RAM parameter to 0 or 1,

ignore this signal.

3

Unused

—

Reserved for future use.

4

Test sine generator

enable

RW

When set to 1b, this bit ignores the audio inputs and uses the output

of the sine generator as the data for each audio group.

7:5

Unused

—

Reserved for future use.