Receiver transceiver interface, Receiver transceiver interface –24, Hd-sdi two-times oversampling – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 54: Sd-sdi transmitter oversampling, Sd-sdi receiver oversampling, Transceiver controller

3–24

Chapter 3: Functional Description

Block Description

Serial Digital Interface (SDI) MegaCore Function

February 2013

Altera Corporation

User Guide

For SD-SDI, the FIFO buffer also provides the rate conversion required by the

transmitter oversampling logic. It is written on every other tx_pclk, using the SD-SDI

data width conversion logic. It is read on every fifth or eleventh tx_coreclk. This

operation ensures that the transmitter oversampling logic is provided with a word of

parallel video data on every fifth or eleventh clock.

HD-SDI Two-Times Oversampling

This mode performs two-times oversampling and runs the transceiver at double rate,

which gives better output jitter performance. This mode requires a higher rate

reference clock, refer to

SD-SDI Transmitter Oversampling

SD-SDI requires a 270-Mbps serial data rate, which is achieved by transmitting a

1,350 Mbps signal with each bit repeated five times. This process ensures that the

transceiver runs at a supported frequency. In triple standard mode, bit are transmitted

at 2,970 Mbps with each bit repeated 11 times.

Receiver Transceiver Interface

Altera provides a transceiver interface, which interfaces the transceiver to the SDI

function. The transceiver interface implements the following functions:

■

■

SD-SDI Receiver Oversampling

Arria GX and Stratix II GX transceivers do not support CDR for data rates less than

622 Mbps. Arria II GX, Arria V, Stratix IV, and Stratix V transceivers do not support

CDR for data rates less than 600 Mbps. The receiver uses fixed frequency

oversampling for the reception of 270-Mbps SD-SDI. The transceiver samples the

serial data at 1,350 or 2,970 Mbps and the SD-SDI receiver oversampling logic extracts

the original 270 Mbps data.

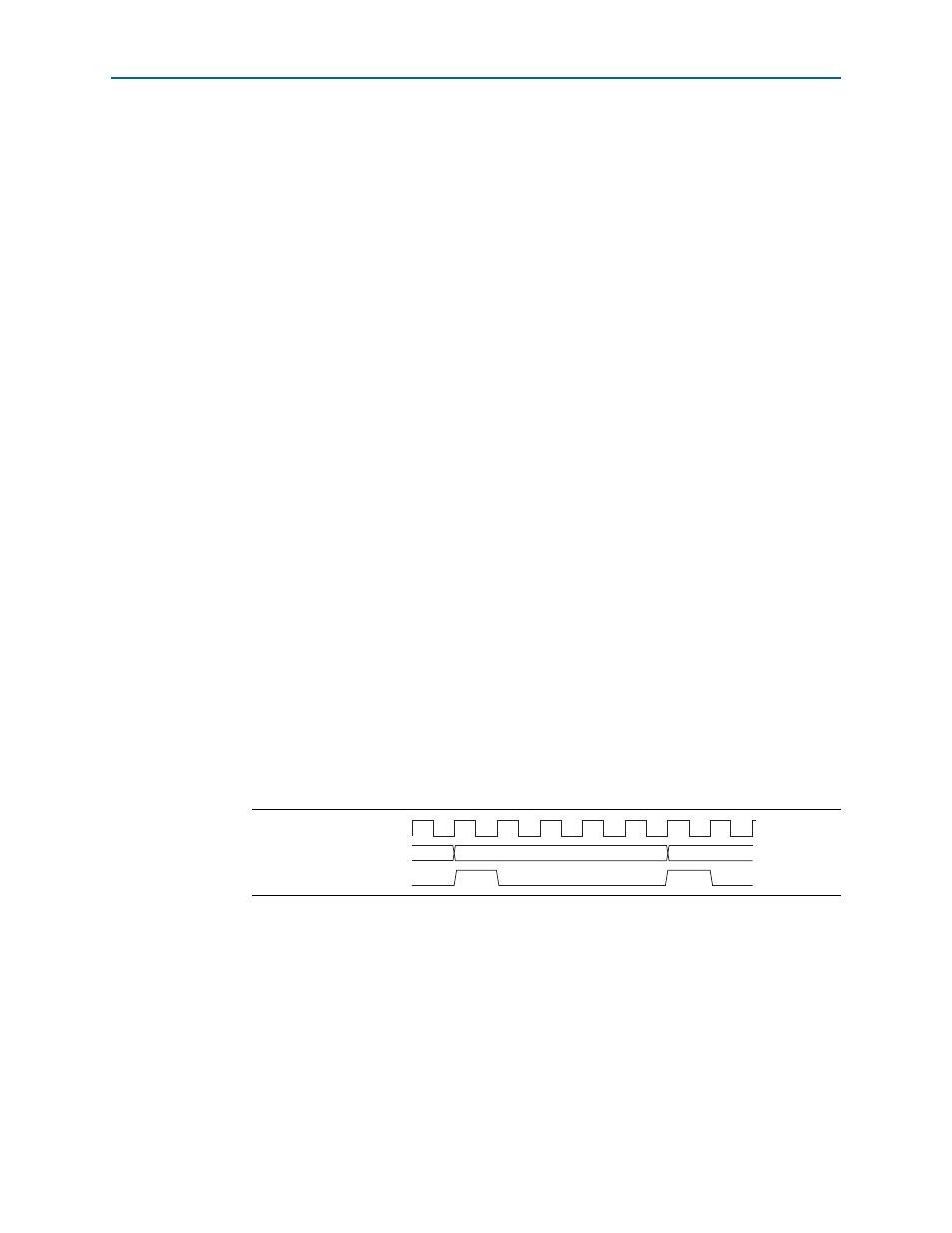

shows an example of the receiver data timing.

Transceiver Controller

To achieve the desired receiver functionality for the SDI, the transceiver controller

controls the transceiver.

When the interface receives SD-SDI, the transceiver receiver PLL locks to the receiver

reference clock.

When the interface receives HD-SDI, the transceiver receiver PLL is first trained by

locking to the receiver reference clock. When the PLL is locked, it can then track the

actual receiver data rate. If a period of time passes without a valid SDI signal, the PLL

is retrained with the reference clock and the process is repeated.

Figure 3–13. Receiver Data Timing

rx_clk (67.5MHz)

rxdata

rx_data_valid_out

DATA