Opencore plus time-out behavior, Signals, Opencore plus time-out behavior –39 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 69: Signals –39, Opencore

Chapter 3: Functional Description

3–39

Signals

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

3. Copy and modify the .mif files for the HD-SDI ROMs and edit word 23.

4. Set the appropriate ROMs to use the .mif files generated in steps

and

.

5. Run the Quartus II compilation.

For Arria II GX and Stratix IV devices, you must set the ROMs to use the fixed .mif in

the example\a2gx_tr\source\sdi_dprio_siv directory and compile once. Ensure that

you use the supporting reconfiguration code in the same directory for your design.

OpenCore Plus Time-Out Behavior

OpenCore Plus hardware evaluation can support the following two modes of

operation:

■

Untethered—the design runs for a limited time

■

Tethered—requires a connection between your board and the host computer. If

tethered mode is supported by all megafunctions in a design, the device can

operate for a longer time or indefinitely

All megafunctions in a device time out simultaneously when the most restrictive

evaluation time is reached. If there is more than one megafunction in a design, a

specific megafunction’s time-out behavior may be masked by the time-out behavior of

the other megafunctions.

1

For MegaCore functions, the untethered time-out is 1 hour; the tethered time-out

value is indefinite.

Your design stops working after the hardware evaluation time expires and the rst

signal goes high.

f

For more information on OpenCore Plus hardware evaluation, refer to

an

Signals

lists the receiver clock signals.

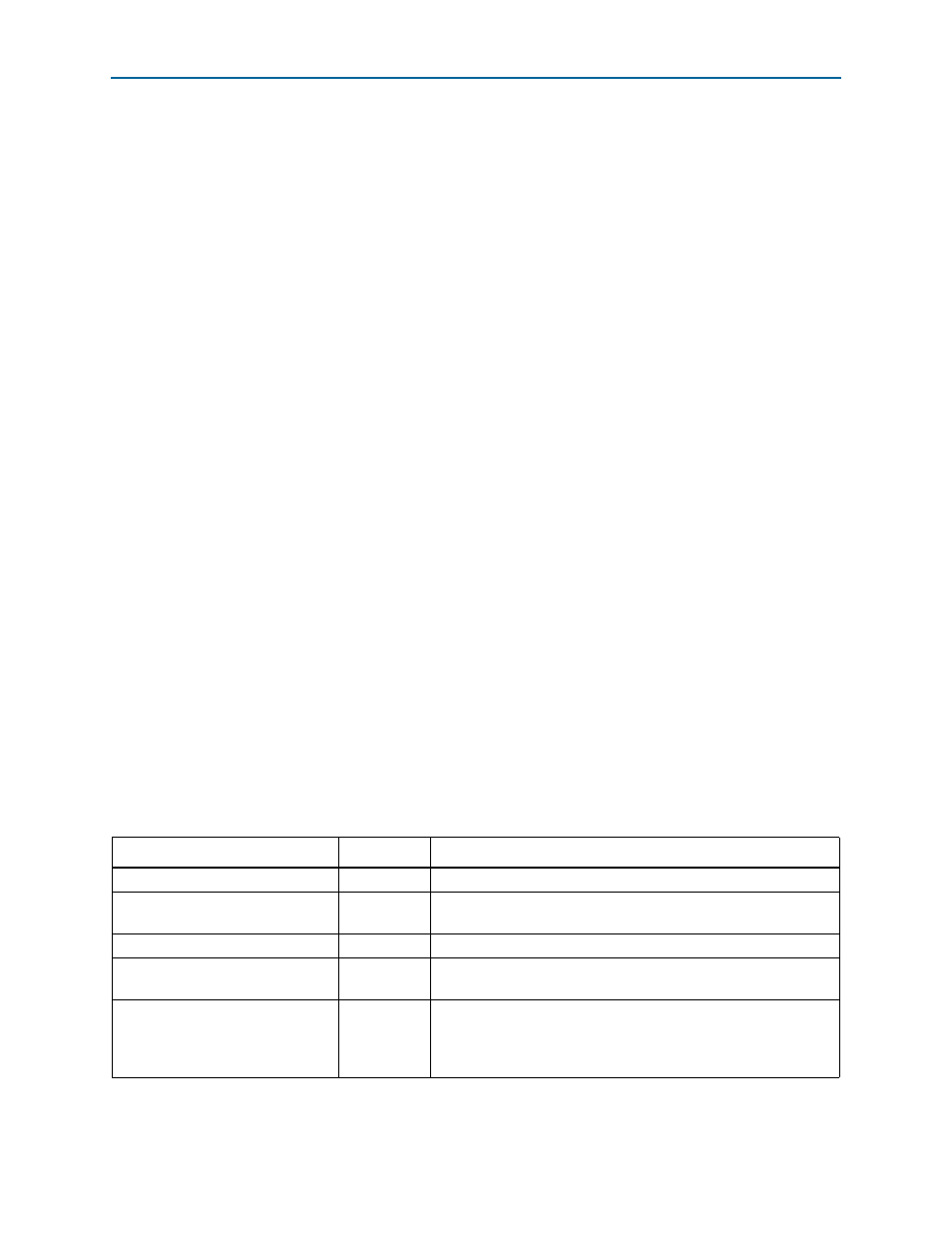

Table 3–12. Receiver Clock Signals (Part 1 of 2)

Signal

Direction

Description

gxb2_cal_clk

Input

Calibration clock for Arria GX and Stratix II GX transceivers only.

gxb4_cal_clk

Input

Calibration clock for Arria II GX, Arria V, Cyclone IV GX,

HardCopy IV, and Stratix IV transceivers only.

rx_sd_oversample_clk_in

Input

67.5-MHz oversample clock input. SD-SDI only.

rx_serial_refclk

Input

Transceiver training clock for HD-SDI, dual standard and triple

standard.

rx_serial_refclk1

Input

Secondary transceiver training clock. Clock frequency of

74.175 MHz for HD-SDI, or clock frequency of 148.35 MHz for

3G-SDI, dual standard and triple standard. Available only when you

use a Cyclone IV GX device.