Als in, Table 4–15, Appe – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 102

4–14

Chapter 4: SDI Audio IP Cores

SDI Audio Extract MegaCore Function

Serial Digital Interface (SDI) MegaCore Function

February 2013

Altera Corporation

User Guide

shows the direct control interface signals. The direct control interface is

internal to the audio extract component.

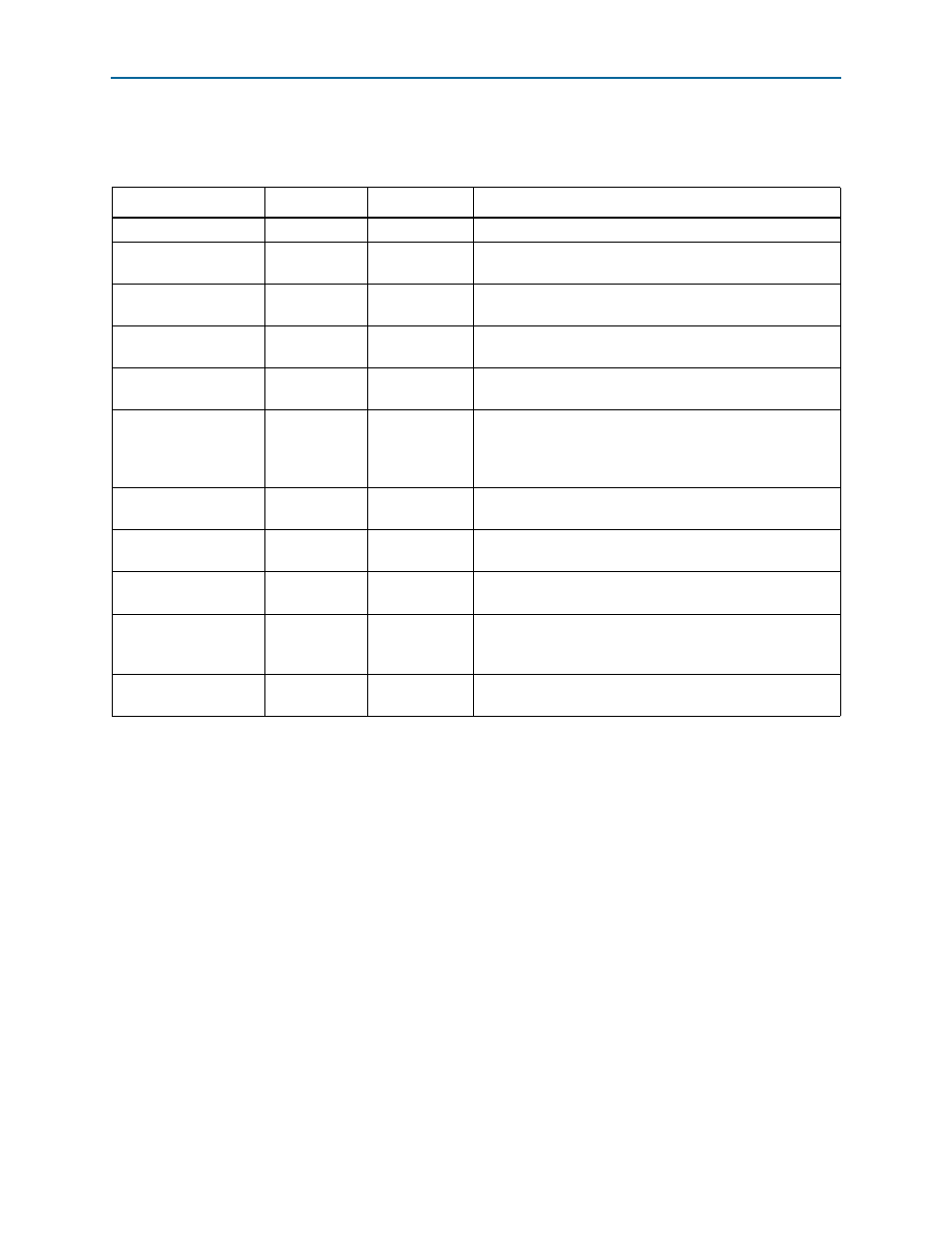

Table 4–15. Direct Control Interface Signals

Signal

Width

Direction

Description

reg_clk

[0:0]

Input

Clock for direct control interface signals.

audio_control

[7:0]

Input

This signal does the same function as the audio control

register in

.

audio_presence

[7:0]

Output

This signal does the same function as the audio presence

register in

.

audio_status

[7:0]

Output

This signal does the same function as the audio status

register in

.

error_status

[7:0]

Output

This signal does the same function as the error status

register in

.

error_reset

[7:0]

Input

Set any bit of this port high for a single cycle of reg_clk to

clear the corresponding bit of the error_status signal.

Setting any of bits [3:0] high for a clock cycle resets the

entire 4-bit error counter.

fifo_status

[7:0]

Output

This signal does the same function as the FIFO status register

in

.

fifo_reset

[0:0]

Input

Set high for a single cycle of reg_clk to clear the underflow

or overflow field of the fifo_status signal.

clock_status

[7:0]

Output

This signal does the same function as the clock status

register in

.

csram_addr

[5:0]

Input

Channel status RAM address. The contents of the selected

address will be valid on the csram_data signal after one

cycle of reg_clk.

csram_data

[7:0]

Output

Channel status data. This signal does the same function as

the channel status RAM in

.