Figure 3–32, Refer to, Figure 3–33 – Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 78: Figure 3–34, Figure 3–35

3–48

Chapter 3: Functional Description

Signals

Serial Digital Interface (SDI) MegaCore Function

February 2013

Altera Corporation

User Guide

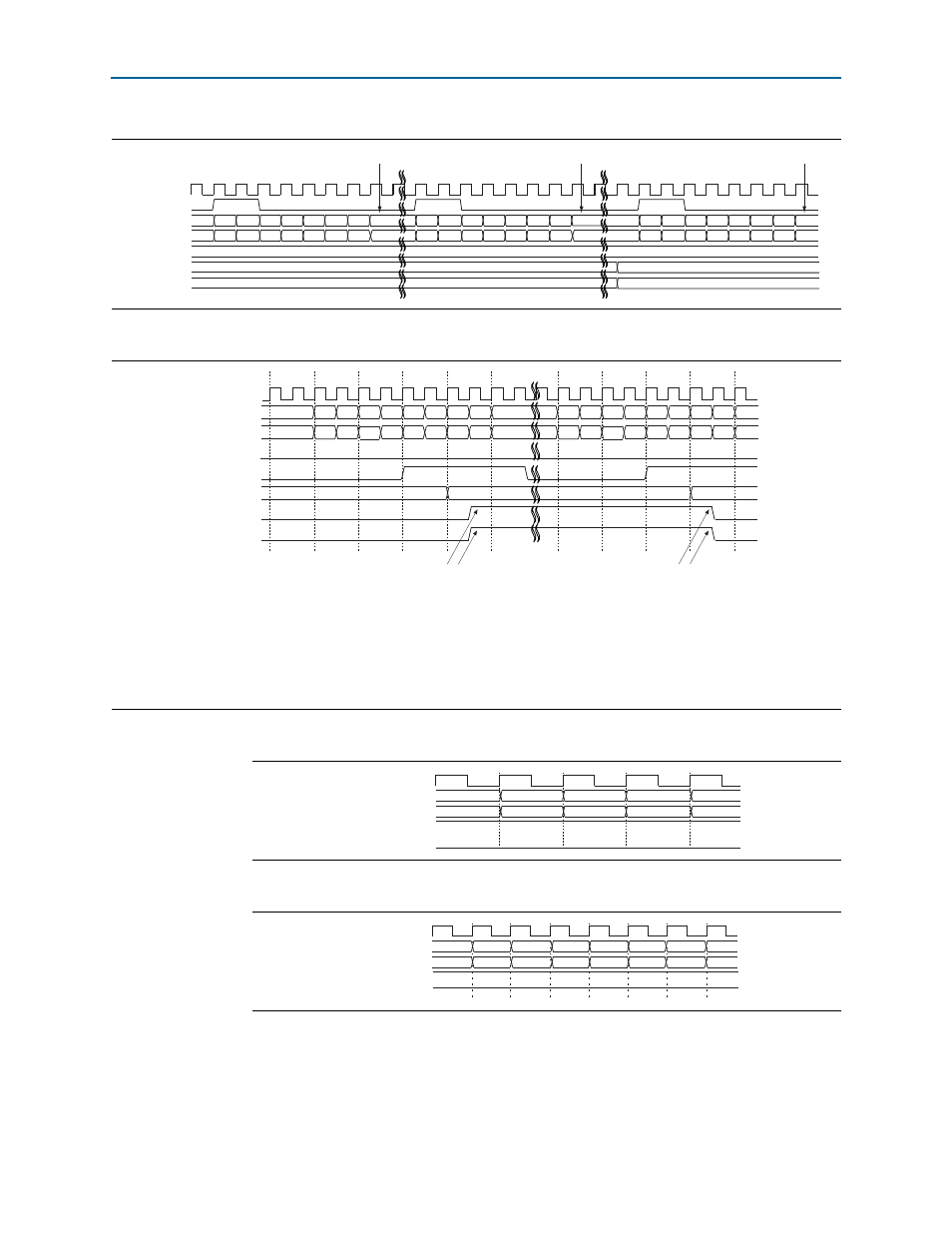

Figure 3–32. Behavior of tx_std, tx_trs, and tx_ln Signals—425MB

tx_pclk

EAV

SAV

EAV

tx_trs

txdata[19:10]

txdata[9:0]

3FF(C) 3FF(Y) 000(C) 000(Y) 000(C) 000(Y) XYZ(C) XYZ(Y)

3FF(C) 3FF(Y) 000(C)

10

000(Y) 000(C) 000(Y) XYZ(C) XYZ(Y)

tx_std[1:0]

tx_ln[21:11]

tx_ln[10:0]

3FF(C) 3FF(Y) 000(C) 000(Y) 000(C) 000(Y) XYZ(C) XYZ(Y)

3FF(C) 3FF(Y) 000(C) 000(Y) 000(C) 000(Y) XYZ(C) XYZ(Y)

3FF(C) 3FF(Y) 000(C) 000(Y) 000(C) 000(Y) XYZ(C) XYZ(Y)

3FF(C) 3FF(Y) 000(C) 000(Y) 000(C) 000(Y) XYZ(C) XYZ(Y)

11’d2

11’d3

11’d4

11’d1

Figure 3–33. Behavior of crc_error_y and crc_error_c Signals

Notes to

:

(1) When a CRC error occurs, the crc_error_y or crc_error_c signal goes high until the next line. For HD, Dual Link, and 3G Level A, only

crc_error_y[0]

and crc_error_c[0] signals are used. For 3G Level B, crc_error_y[0]and crc_error_c[0] signals are used for link B,

and crc_error_y[1]and crc_error_c[1] signals are used for link A.

(2) The CRC error signals are asserted after the CRC data checked, when the rx_H signal is high. A high CRC signal indicates that there is error in the

previous line data. In this case, both Y and C have CRC error.

(3) The CRC error signals are deasserted on the next line after the CRC data is checked.

rx_clk

rxdata[19:0]

crc_error_c

rxdata[9:0]

rx_V

rx_H

rx_ln

crc_error_y

000

000

000

3FF

XYZ

CRC1 CRC2

LN1

LN2

XYZ

CRC1 CRC2

LN1

LN2

000

3FF

000001a

000

000

000

3FF

XYZ

CRC1 CRC2

LN1

LN2

XYZ

CRC1 CRC2

LN1

LN2

000

3FF

000001b

(2)

(3)

Figure 3–34. Behavior of rx_data_valid Signal—425MA

Figure 3–35. Behavior of rx_data_valid Signal—425MB

rx_clk (148.5 MHz)

rxdata[19:10]

rxdata[9:0]

rx_data_valid_out[0]

rx_data_valid_out[1]

3FF(Y)

000(Y)

000(Y)

XYZ(Y)

000(Y)

3FF(C)

000(C)

000(C)

XYZ(C)

000(C)

rx_clk (148.5 MHz)

rxdata[19:10]

rxdata[9:0]

rx_data_valid_out[0]

rx_data_valid_out[1]

3FF(C)

3FF(Y)

000(C)

000(Y)

000(C)

000(Y)

XYZ(C)

000(Y)

3FF(C)

3FF(Y)

000(C)

000(Y)

000(C)

000(Y)

XYZ(C)

000(Y)