Altera Serial Digital Interface (SDI) MegaCore Function User Manual

Page 21

Chapter 2: Getting Started

2–7

SDI Walkthrough

February 2013

Altera Corporation

Serial Digital Interface (SDI) MegaCore Function

User Guide

describes the generated files and other files that may be in your project

directory. The names and types of files specified in the MegaWizard Plug-In Manager

report vary based on whether you created your design with VHDL or Verilog HDL.

You can now integrate your custom MegaCore function variation into your design,

simulate, and compile.

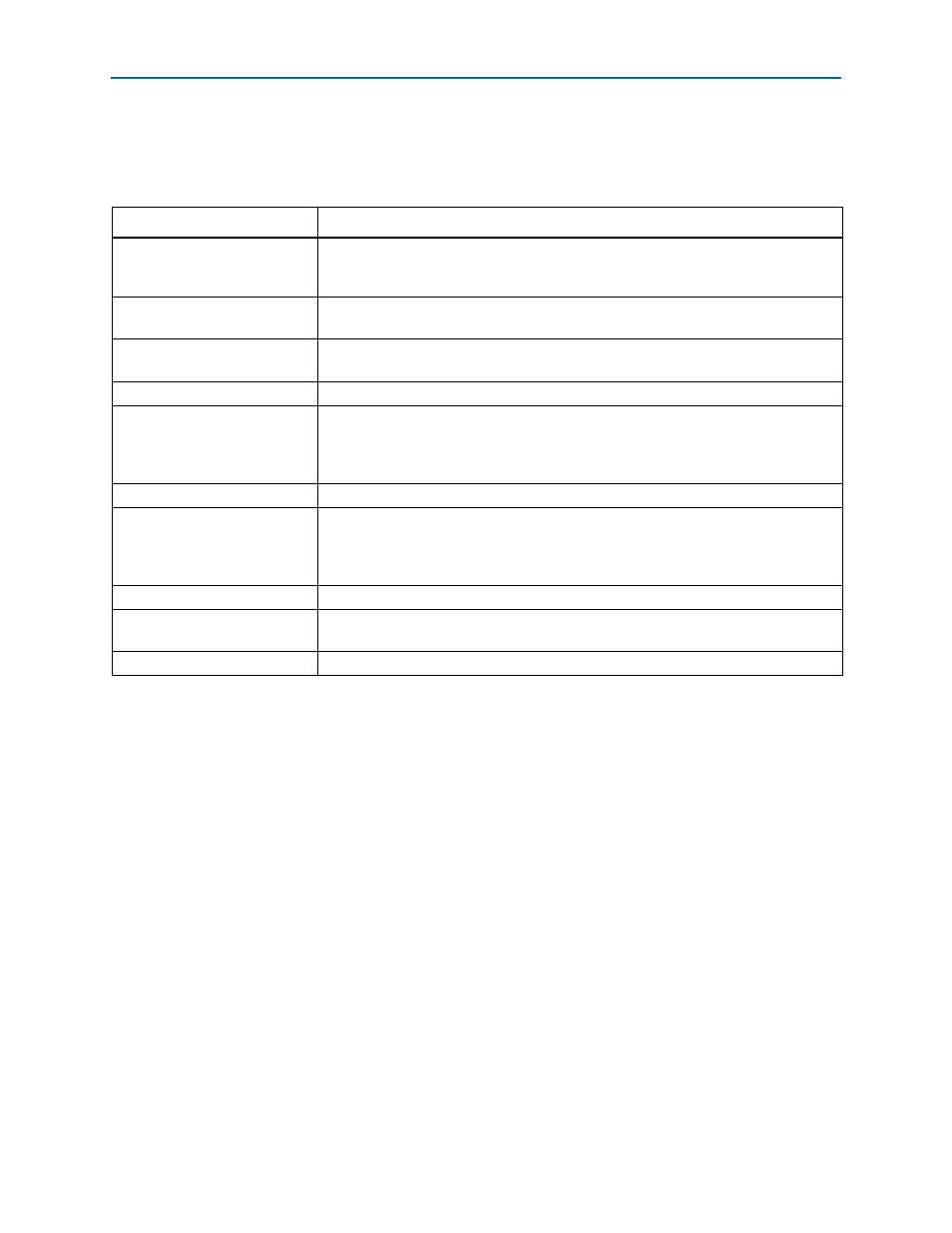

Table 2–1. Generated Files

Extension

Description

<variation name>.v or .vhd

A MegaCore function variation file, which defines a VHDL or Verilog HDL description of

the custom MegaCore function. Instantiate the entity defined by this file inside of your

design. Include this file when compiling your design in the Quartus II software.

<variation name>.cmp

A VHDL component declaration file for the MegaCore function variation. Add the

contents of this file to any VHDL architecture that instantiates the MegaCore function.

<variation name>.bsf

Quartus II symbol file for the MegaCore function variation. You can use this file in the

Quartus II block diagram editor.

<variation name>.html

MegaCore function report file.

This XML file describes the MegaCore pin attributes to the Quartus II Pin Planner.

MegaCore pin attributes include pin direction, location, I/O standard assignments, and

drive strength. If you launch IP Toolbench outside of the Pin Planner application, you

must explicitly load this file to use Pin Planner.

<variation name>_sdi.sdc

Contains timing constraints for your SDI variation.

<variation name>_constraints.tcl

Quartus II file that sets the Quartus II to use TimeQuest timing analyzer and patches the

generated .sdc script with a new clock name. If your top-level design clock pin names do

not match the default clock pin names or a prefixed version, edit the assignments in this

file.

<variation name>.vo or .vho

VHDL or Verilog HDL IP functional simulation model.

<variation name>_bb.v

A Verilog HDL black-box file for the MegaCore function variation. Use this file when

using a third-party EDA tool to synthesize your design.

<variation name>.qip

Contains Quartus II project information for your MegaCore function variations.